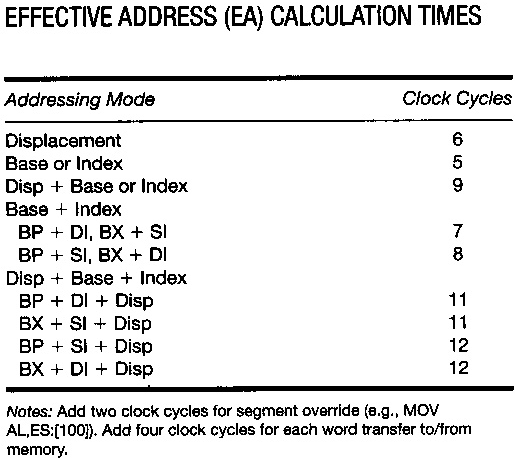

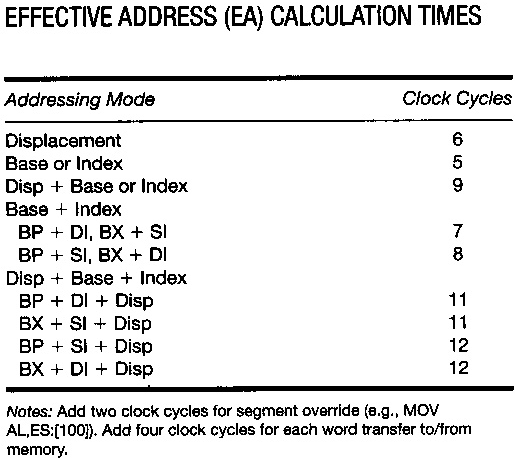

Effective address calculation times:

| <<< Relation of Base Registers to Memory Segments | Index | >>> |

Immediate Mode (memory is not accessed) - operand is part of the instruction. For example, a constant encoded in the instruction:

mov eax,567

mov ah, 09h

mov dx, offset Prompt

Register Addressing (memory is not accessed) - operand contained in register:

add ax, bx

Direct Mode (memory accessed once) - operand field of instruction contains address of the operand:

value dword 0

..

add eax, value ; Either notation does the

add eax, [value] ; same thing

Assembly code

tbl DW 20 DUP (0)

..

mov [tbl], 56

is equivalent to C statement

tbl[ 0 ] = 56; // C code

register indirect addressing (aka indirect addressing mode) often used for addressing data arrays inside programming loops:

Effective address of operand contained in a register.

For 32-bit addressing, all 32-bit registers can be used.

For 16-bit addressing, the offset value can be in one of the three registers: BX, SI, or DI:

mov bx, offset Table ; Load address

add ax, [bx] ; Register indirect addressing

Square brackets [ BX ] indicate that BX is holding a memory offset.

Operand [ BX ] serves as a pointer to data in memory.

Register indirect can be used to implement arrays. For example, to sum an array of word-length integers,

mov cx, size ; set up size of Table

mov bx, offset Table ; BX <- address of Table

xor ax, ax ; zero out Sum

Loop1:

add ax, [bx]

inc bx ; each word is 2 bytes long, so

inc bx ; need to increment BX twice!

loop Loop1

Indexing: constant base + register.

Fixed Base (address) + Variable Register Offset (operand field contains a constant base)

Effective address is obtained by adding value of operand field to contents of register.

This is known as array type addressing, also called displacement addressing.

mov eax, [ ebx + 5 ]

mov eax, [ ebx + esi + 5 ]

There are restrictions on the combinations of registers allowed within the brackets: you can have ESI or EDI, but not both, and you can have EBX or EBP, but not both.

The following instructions are equivalent:

add ax, Table[ bx ]

add ax, [ Table + bx ]

add ax, Table + [ bx ]

add ax, [ bx ] + Table

Indexing With Scaling: Base + Register Offset * Scaling Factor

Operand field contains base address.

Useful for array calculations where size of component is multiple bytes long.

Stack Addressing: PUSH and POP, a variant of register indirect with auto-increment/decrement using the ESP register implicitly.

Jump relative addressing, EIP + offset

Operand field contains a displacement.

Used by near and short jump instructions on the Intel 80x86. see also:

Effective address calculation times:

| <<< Relation of Base Registers to Memory Segments | Index | >>> |