|

Keyword

|

Description

|

|

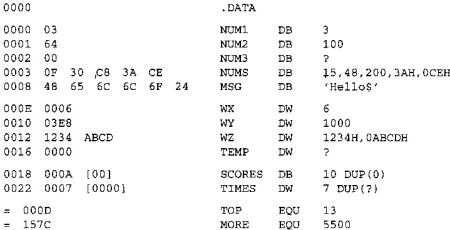

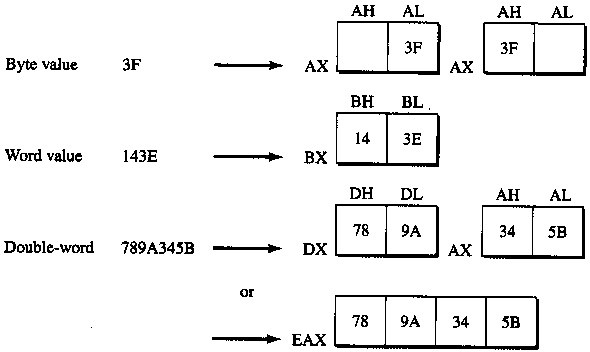

BYTE, DB (byte)

|

Allocates unsigned numbers from 0 to 255.

|

|

SBYTE (signed byte)

|

Allocates signed numbers from 128 to +127.

|

|

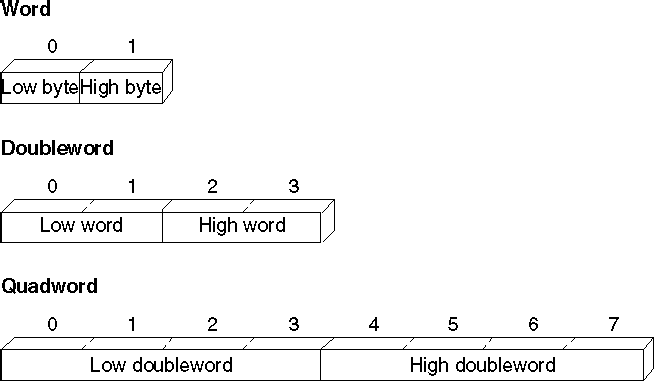

WORD, DW (word = 2 bytes)

|

Allocates unsigned numbers from 0 to 65,535 (64K).

|

|

SWORD (signed word)

|

Allocates signed numbers from 32,768 to +32,767.

|

|

DWORD, DD (doubleword = 4 bytes)

|

Allocates unsigned numbers from 0 to 4,294,967,295 (4 megabytes)

|

|

SDWORD (signed doubleword)

|

Allocates signed numbers from 2,147,483,648 to +2,147,483,647.

|

|

FWORD, DF (farword = 6 bytes)

|

Allocates 6-byte (48-bit) integers. These values are normally used only as pointer

variables on the 80386/486 processors.

|

|

QWORD, DQ (quadword = 8 bytes)

|

Allocates 8-byte integers used with 8087-family coprocessor instructions.

|

|

TBYTE, DT (10 bytes)

|

Allocates 10-byte (80-bit) integers if the initializer has a radix specifying the

base of the number.

|

-

Sign extending instructions efficiently convert unsigned values as well, provided the sign bit is zero.

-

This example, for instance, correctly widens mem16 whether you treat the variable as signed or unsigned.

-

The processor does not differentiate between signed and unsigned values.

-

For instance, the value of mem8 in the previous example is literally 251 (0FBh) to the processor.

-

It ignores the human convention of treating the highest bit as an indicator of sign.

-

The processor can ignore the distinction between signed and unsigned numbers because binary arithmetic works the same in either case.

-

The programmer, not the processor, must keep track of which values are signed or unsigned, and treat them accordingly.