-

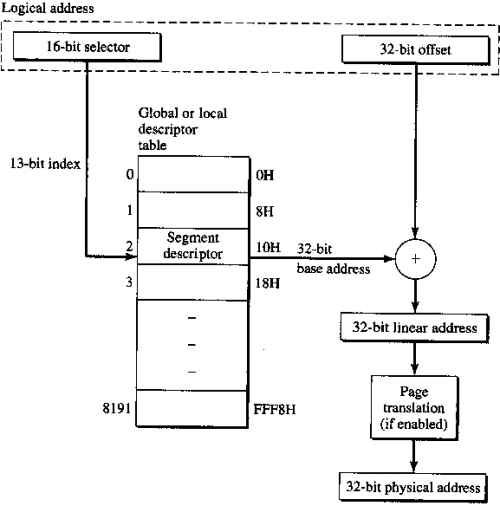

The 32-bit base address obtained from the descriptor entry is added to the memory offset to obtain a 32-bit linear address.

-

If virtual memory mode is enabled, the linear address of the segment is interpreted as a 20-bit page number and a 12-bit page offset.

-

The 386 uses a two-level paging scheme, thus dividing the page number into 10-bit page-table directory pointer and a 10-bit page table pointer.