-

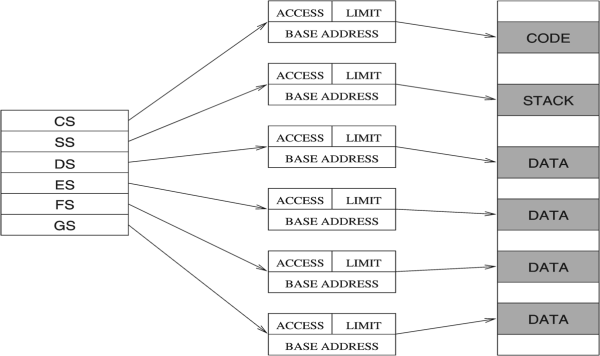

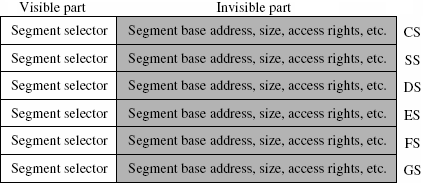

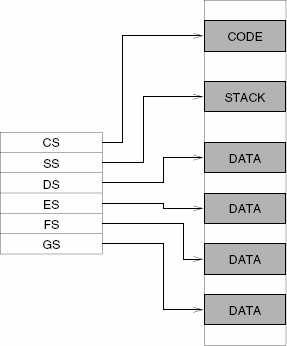

Segment Registers in Protected Mode separate different blocks of code and data to protect them from undesirable interactions.

-

CS (Code Segment) contains processor instructions and their immediate operands.

-

DS (Data Segment) normally contains data allocated by the program.

-

SS (Stack Segment) contains the program stack for use by PUSH, POP, CALL, and RET.

-

ES (Extra Segment) references secondary data segment. Used by string instructions.

-

FS, GS provide extra segments on 80386/486/Pentium.

-

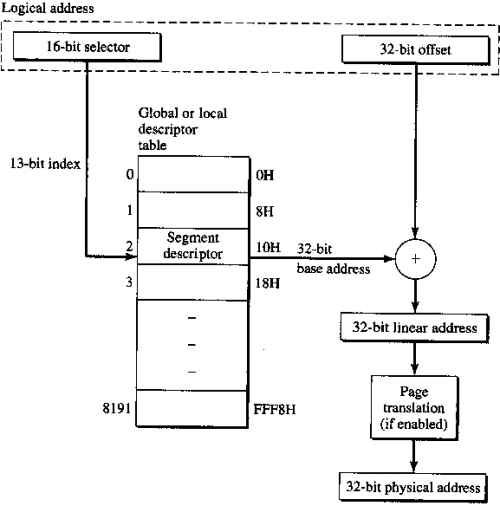

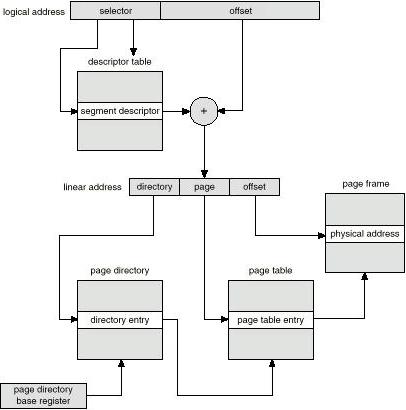

The six segments of the memory system:

Segmented architecture is an important part of Linux and Windows memory-protection schemes.