-

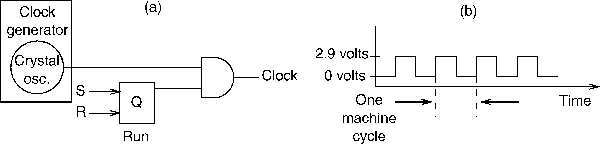

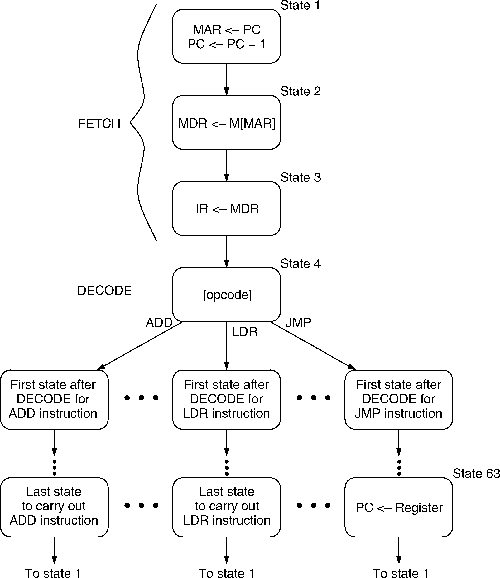

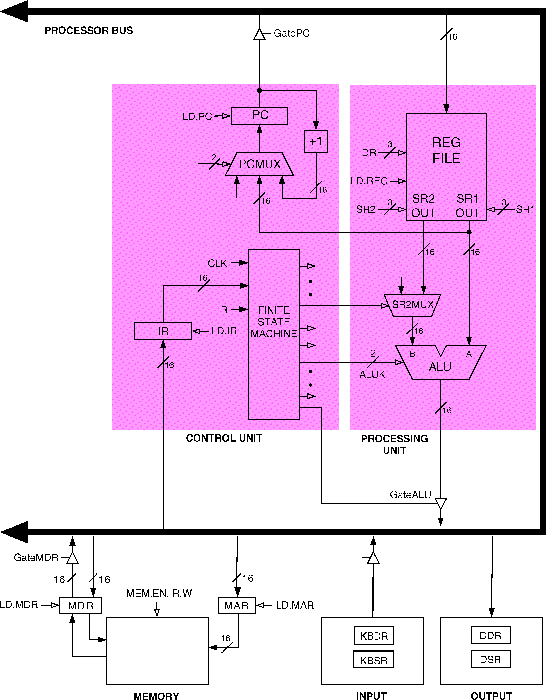

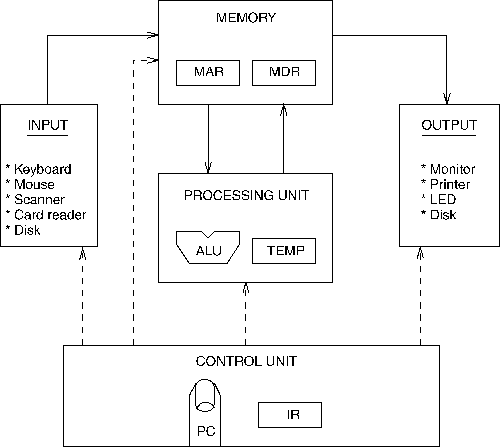

Instructions are processed under direction of the control unit in step-by-step manner.

-

Each step is referred to as a phase.

-

There are six fundamental phases of the instruction cycle:

-

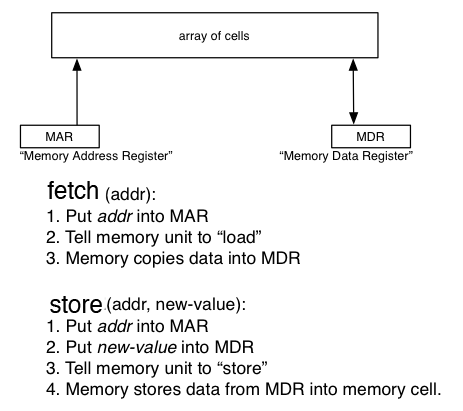

fetch instruction (aka pre-fetch)

-

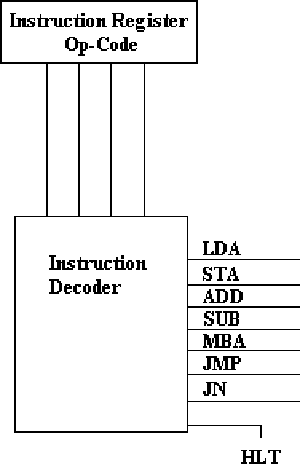

decode instruction

-

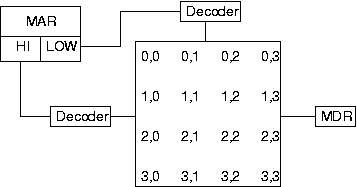

evaluate address (address generation)

-

fetch operands (read memory data)

-

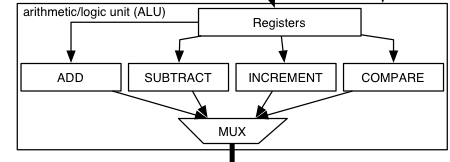

execute (ALU access)

-

store result (writeback memory data)

-

-

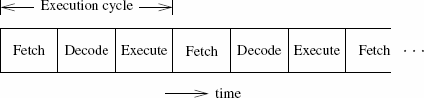

Instruction cycle:

-

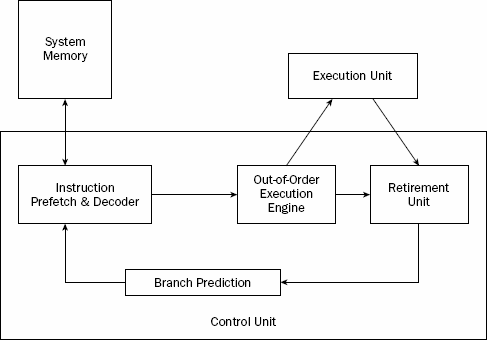

Pentium 4 instruction cycle: