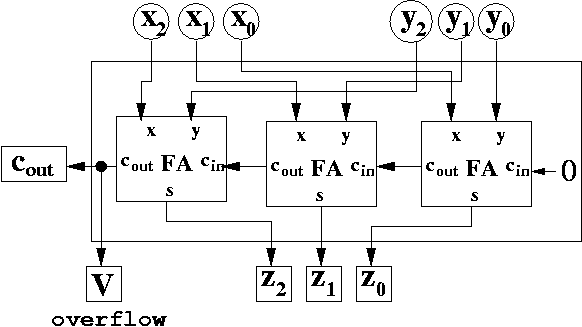

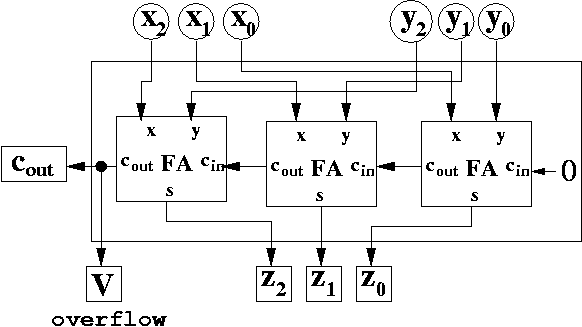

Overflow detection circuit for unsigned binary addition:

CIS-77 Home http://www.c-jump.com/CIS77/CIS77syllabus.htm

Arithmetic operations have a potential to run into a condition known as overflow.

Overflow occurs with respect to the size of the data type that must accommodate the result.

Overflow indicates that the result was too large or too small to fit in the original data type.

When two signed 2's complement numbers are added, overflow is detected if:

both operands are positive and the result is negative, or

both operands are negative and the result is positive.

When two unsigned numbers are added, overflow occurrs if

there is a carry out of the leftmost bit.

Computers don't know the difference between signed and unsigned binary numbers.

This is a good thing, because it makes logic circuits fast.

This is also a bad thing, because distinguishing between signed and unsigned is our responsibility.

The distinction is very important when detecting an overflow after addition or subtraction.

Correct approach to detect the overflow is to consider two separate cases:

Overflow when adding unsigned numbers.

Overflow when adding signed numbers.

Let's first solve the problem for addition of one-bit quntities:

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

The last line indicates that we have a carry output.

That is, one-bit quantity cannot accommodate (1 + 1).

Therefore, larger data type is required for (1 + 1) to succeed.

When multi-bit unsigned quantities are added, overflow occurrs if there is a carry out from the leftmost (most significant) bit.

Overflow detection circuit for unsigned binary addition:

Consider overflow detection when adding two one-bit signed quntities.

Although one bit is required to represent the data, another bit has to represent the sign.

Therefore, two-bit data type is required:

|

|

|||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

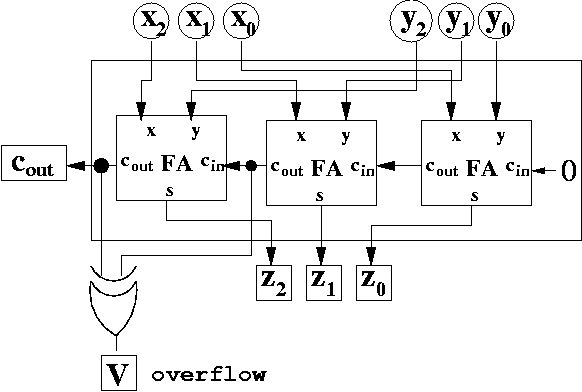

Overflow detection circuit for 2's complement addition

Specific overflow detection requires knowing the operation and the representation.

Overflow occurs when you do some operation to two valid representations...

...and the result can not be represented in the representation because the value is too large or too smal.

Overflow detection is detecting overflow for a specific representation...

...Too often people mistake overflow condition for unsigned overflow, when the carry out is 1.

Overflow detection for 2's complement addition is different:

One way to detect it is to XOR the carry in and the carry out.