-

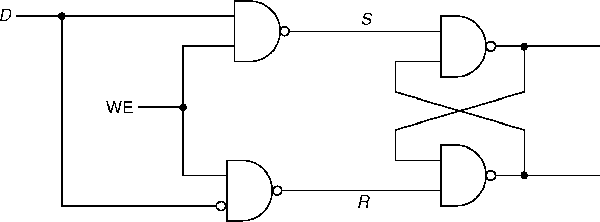

The R-S latch can store one bit of information.

-

Also known as the Basic RS NAND Latch.

-

It works as follows:

-

The inputs are generally designated "S" and "R" for "Set" and "Reset", respectively.

-

Assume that S=1 and R=1.

-

If a=1, then A=1 and b=0 and B=0 and a=1.

-

R-S latch circuit: