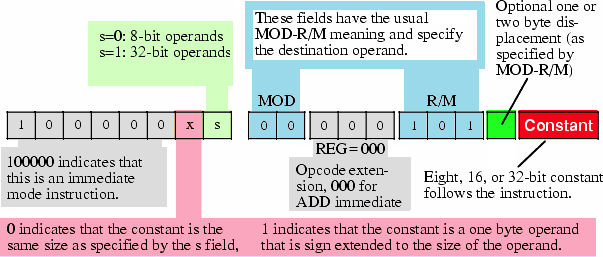

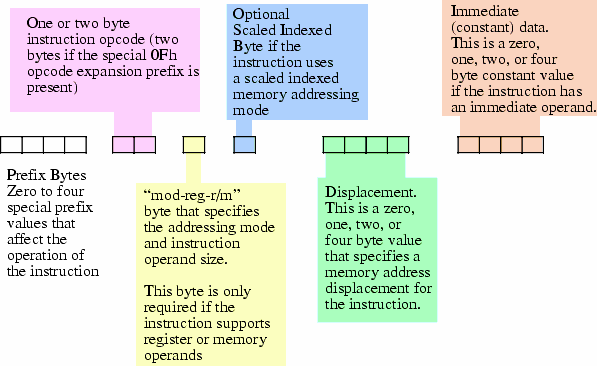

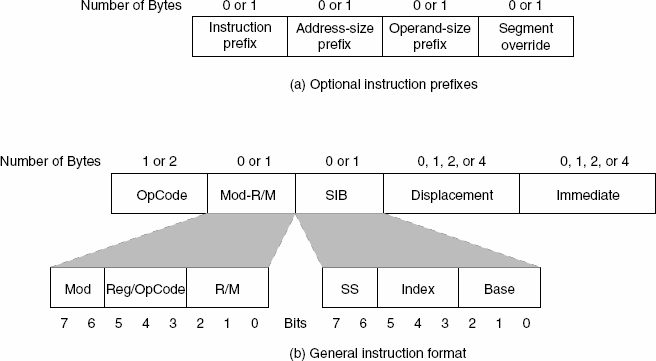

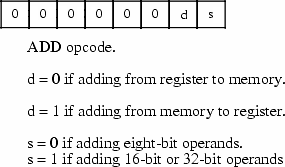

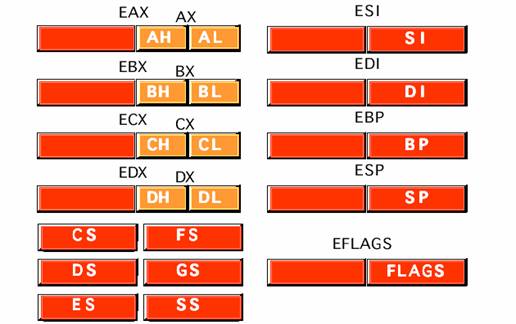

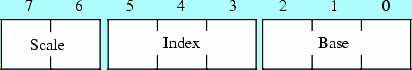

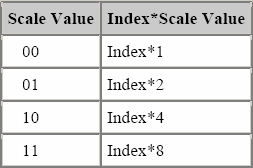

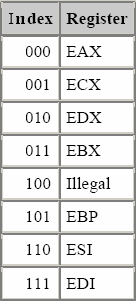

It is time to take a look that the actual machine instruction format of the x86 CPU family.

They don't call the x86 CPU a Complex Instruction Set Computer (CISC) for nothing!

Although more complex instruction encodings exist, no one is going to challenge that the x86 has a complex instruction encoding:

![Encoding the ADD EDI, [EBX] Instruction](http://www.c-jump.com/CIS77/images/encoding_add_edi_ebx.png)

![Encoding the ADD EAX, [ ESI + disp8 ] Instruction](http://www.c-jump.com/CIS77/images/encoding_add_eax_esi_disp8.png)

![Encoding the ADD EBX, [ EBP + disp32 ] Instruction](http://www.c-jump.com/CIS77/images/encoding_add_ebx_ebp_disp32.png)

![Encoding the ADD EBP, [ disp32 + EAX*1 ] Instruction](http://www.c-jump.com/CIS77/images/encoding_add_ebp_disp32_eax_1.png)

![Encoding ADD ECX, [ EBX + EDI*4 ] Instruction](http://www.c-jump.com/CIS77/images/encoding_add_ecx_ebx_edi_4.png)