3-12

INSTRUCTION SET REFERENCE

3.1.5.FPU Flags Affected

The floating-point instructions have an FPU Flags Affected section that describes how each

instruction can affect the four condition code flags of the FPU status word.

3.1.6.Protected Mode Exceptions

The Protected Mode Exceptions section lists the exceptions that can occur when the instruc-

tion is executed in protected mode and the reasons for the exceptions. Each exception is given

a mnemonic that consists of a pound sign (#) followed by two letters and an optional error code

in parentheses. For example, #GP(0) denotes a general protection exception with an error code

of 0. Table 3-2 associates each two-letter mnemonic with the corresponding interrupt vector

number and exception name. Refer to Chapter 5, Interrupt and Exception Handling, of the Intel

Architecture Software Developers Manual, Volume 3, for a detailed description of the excep-

tions.

Application programmers should consult the documentation provided with their operating

systems to determine the actions taken when exceptions occur.

3.1.7.Real-Address Mode Exceptions

The Real-Address Mode Exceptions section lists the exceptions that can occur when the

instruction is executed in real-address mode.

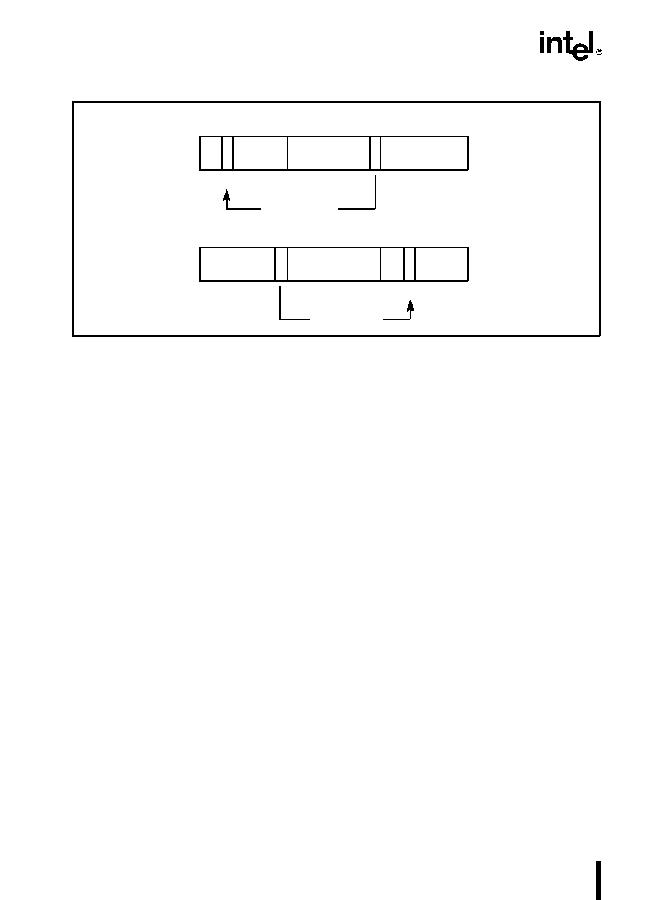

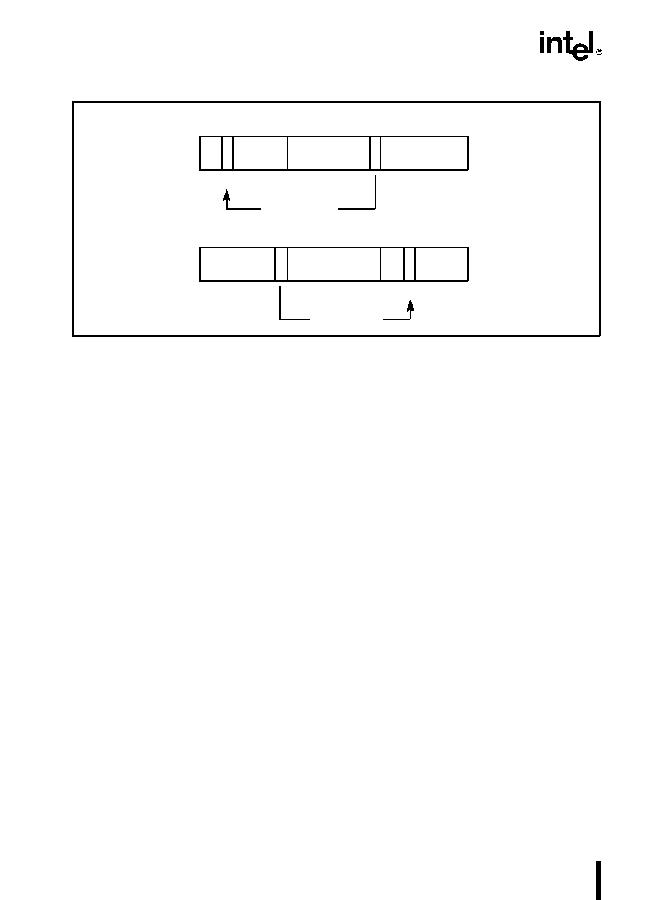

Figure 3-2. Memory Bit Indexing

BitBase + 1

0

7

7

75

0

0

BitBase

?

2

0

7

7

7

5

0

0

BitBase

BitBase

?

1

BitOffset = +13

BitOffset =

?

11

BitBase

?

1

BitBase