3-111

INSTRUCTION SET REFERENCE

CPUIDCPU Identification

Description

This instruction provides processor identification information in registers EAX, EBX, ECX, and

EDX. This information identifies Intel as the vendor, gives the family, model, and stepping of

processor, feature information, and cache information. An input value loaded into the EAX

register determines what information is returned, as shown in Table 3-6.

The CPUID instruction can be executed at any privilege level to serialize instruction execution.

Serializing instruction execution guarantees that any modifications to flags, registers, and

memory for previous instructions are completed before the next instruction is fetched and

executed. For more information, refer to Section 7.4., Serializing Instructions in Chapter 7,

Multiple-Processor Management of the Intel Architecture Software Developers Manual,

Volume 3.

When the input value in register EAX is 0, the processor returns the highest value the CPUID

instruction recognizes in the EAX register (refer to Table 3-6). A vendor identification string is

returned in the EBX, EDX, and ECX registers. For Intel processors, the vendor identification

string is GenuineIntel as follows:

EBX

<

756e6547h (* "Genu", with G in the low nibble of BL *)

EDX

<

49656e69h (* "ineI", with i in the low nibble of DL *)

ECX

<

6c65746eh (* "ntel", with n in the low nibble of CL *)

Opcode

Instruction

Description

0F A2

CPUID

EAX

<

Processor identification information

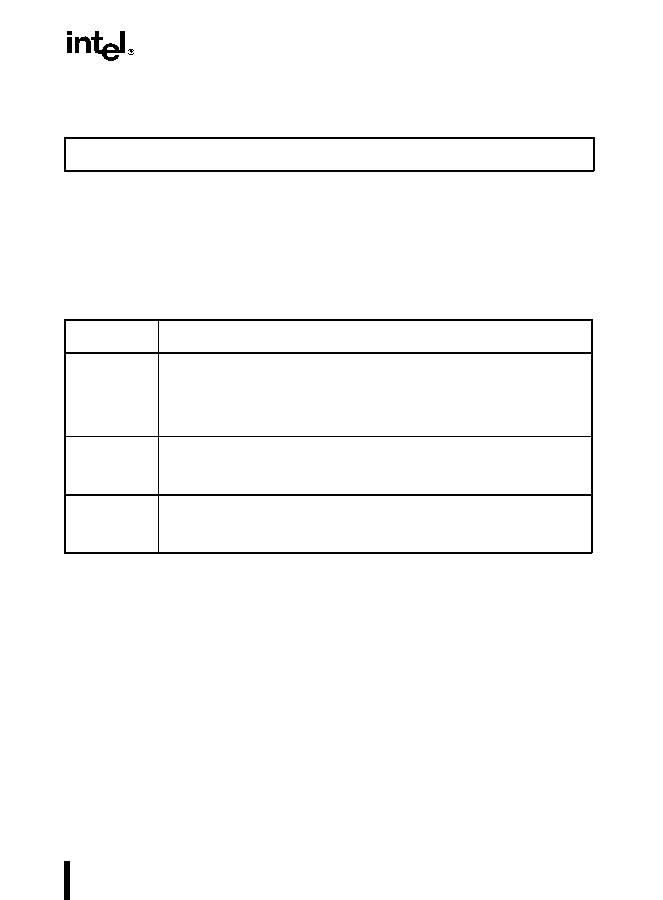

Table 3-6. Information Returned by CPUID Instruction

Initial EAX

Value

Information Provided about the Processor

0

EAX

EBX

ECX

EDX

Maximum CPUID Input Value (2 for the P6 family processors and 1 for the

Pentium

®

processor and the later versions of Intel486 processor that

support the CPUID instruction).

Genu

ntel

ineI

1

EAX

EBX

ECX

EDX

Version Information (Type, Family, Model, and Stepping ID)

Reserved

Reserved

Feature Information

2

EAX

EBX

ECX

EDX

Cache and TLB Information

Cache and TLB Information

Cache and TLB Information

Cache and TLB Information