3-292

INSTRUCTION SET REFERENCE

IDIVSigned Divide

Description

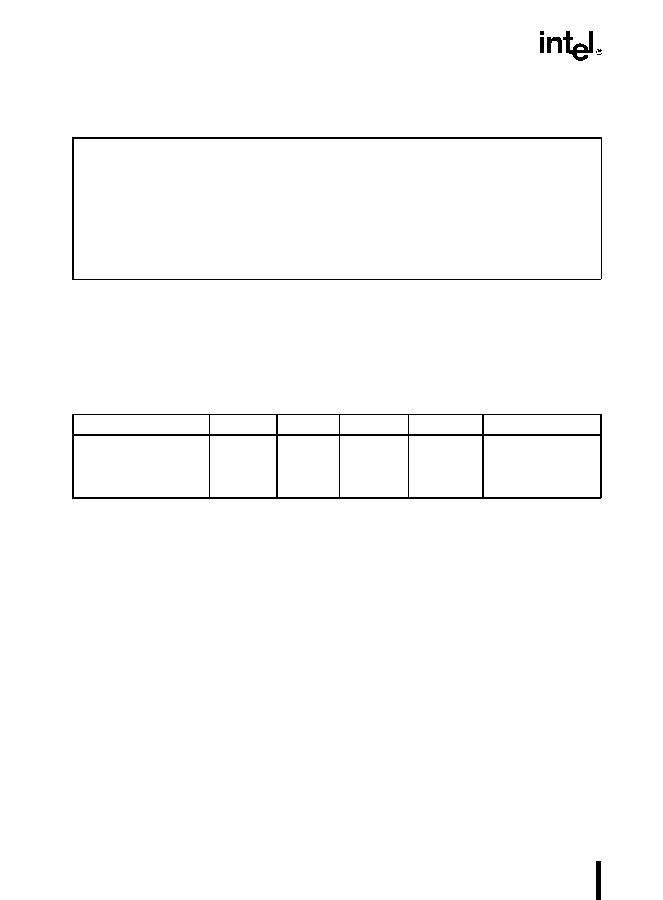

This instruction divides (signed) the value in the AL, AX, or EAX register by the source operand

and stores the result in the AX, DX:AX, or EDX:EAX registers. The source operand can be a

general-purpose register or a memory location. The action of this instruction depends on the

operand size, as shown in the following table:

Non-integral results are truncated (chopped) towards 0. The sign of the remainder is always the

same as the sign of the dividend. The absolute value of the remainder is always less than the

absolute value of the divisor. Overflow is indicated with the #DE (divide error) exception rather

than with the OF (overflow) flag.

Operation

IF SRC = 0

THEN #DE; (* divide error *)

FI;

IF OpernadSize = 8 (* word/byte operation *)

THEN

temp

<

AX / SRC; (* signed division *)

IF (temp > 7FH) OR (temp < 80H)

(* if a positive result is greater than 7FH or a negative result is less than 80H *)

THEN #DE; (* divide error *) ;

ELSE

AL

<

temp;

AH

<

AX SignedModulus SRC;

FI;

Opcode

Instruction

Description

F6 /7

IDIV r/m8

Signed divide AX (where AH must contain sign-

extension of AL) by r/m byte. (Results: AL=Quotient,

AH=Remainder)

F7 /7

IDIV r/m16

Signed divide DX:AX (where DX must contain sign-

extension of AX) by r/m word. (Results: AX=Quotient,

DX=Remainder)

F7 /7

IDIV r/m32

Signed divide EDX:EAX (where EDX must contain

sign-extension of EAX) by r/m doubleword. (Results:

EAX=Quotient, EDX=Remainder)

Operand SizeDividendDivisorQuotientRemainderQuotient Range

Word/byte

AX

r/m8AL

AH

?

128 to +127

Doubleword/word

DX:AXr/m16AX

DX

?

32,768 to +32,767

Quadword/doublewordEDX:EAXr/m32EAX

EDX

?

2

31

to 2

32

?

1