3-345

INSTRUCTION SET REFERENCE

LDMXCSRLoad Streaming SIMD Extension Control/Status

Description

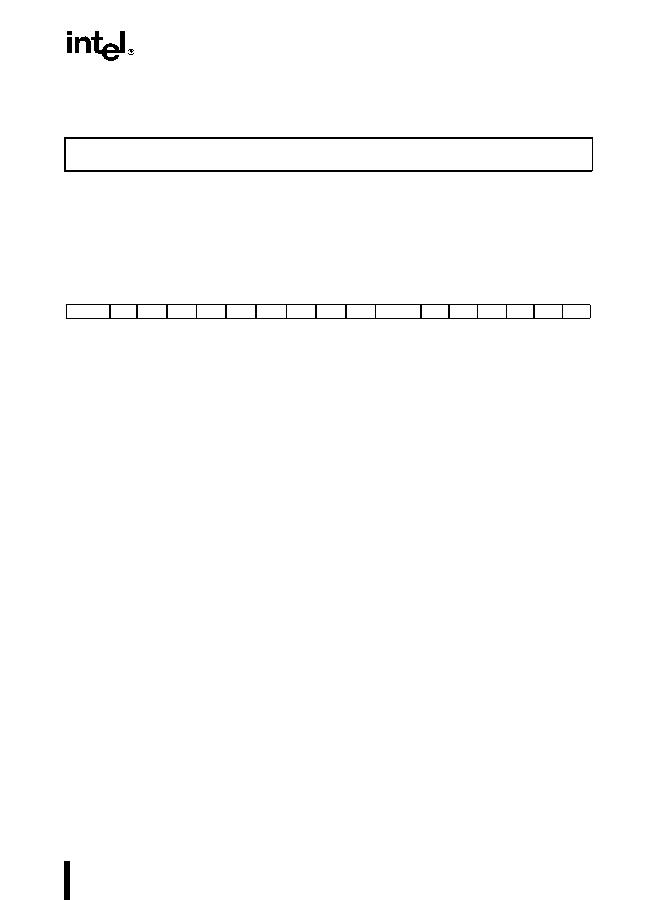

The MXCSR control/status register is used to enable masked/unmasked exception handling, to

set rounding modes, to set flush-to-zero mode, and to view exception status flags. The following

figure shows the format and encoding of the fields in MXCSR:

The default MXCSR value at reset is 0x1f80.

Bits 5-0 indicate whether a Streaming SIMD Extension numerical exception has been detected.

They are sticky flags, and can be cleared by using the LDMXCSR instruction to write zeroes

to these fields. If an LDMXCSR instruction clears a mask bit and sets the corresponding excep-

tion flag bit, an exception will not be immediately generated. The exception will occur only

upon the next Streaming SIMD Extension to cause this type of exception. Streaming SIMD

Extension uses only one exception flag for each exception. There is no provision for individual

exception reporting within a packed data type. In situations where multiple identical exceptions

occur within the same instruction, the associated exception flag is updated and indicates that at

least one of these conditions happened. These flags are cleared upon reset.

Bits 12-7 configure numerical exception masking. An exception type is masked if the corre-

sponding bit is set, and unmasked if the bit is clear. These enables are set upon reset, meaning

that all numerical exceptions are masked.

Bits 14-13 encode the rounding control, which provides for the common round to nearest mode,

as well as directed rounding and true chop. Rounding control affects the arithmetic instructions

and certain conversion instructions. The encoding for RC is as follows:

OpcodeInstructionDescription

0F,AE,/2LDMXCSR m32Load Streaming SIMD Extension control/status word from m32.

31-1615

10

5

0

RsvdFZRCRCPMUMOMZMDMIMRsvdPEUEOEZEDEIE