3-558

INSTRUCTION SET REFERENCE

PSRLW/PSRLD/PSRLQPacked Shift Right Logical

Description

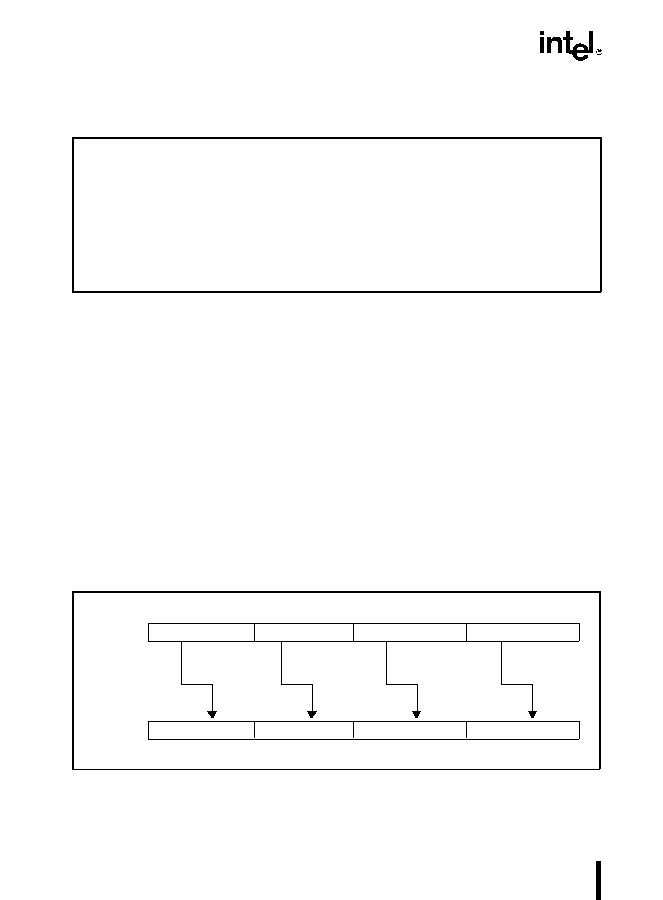

These instructions shift the bits in the data elements (words, doublewords, or quadword) in the

destination operand (first operand) to the right by the number of bits specified in the unsigned

count operand (second operand) (refer to Figure 3-79). The result of the shift operation is written

to the destination operand. As the bits in the data elements are shifted right, the empty high-order

bits are cleared (set to zero). If the value specified by the count operand is greater than 15 (for

words), 31 (for doublewords), or 63 (for a quadword), then the destination operand is set to all

zeroes.

The destination operand must be an MMX technology register; the count operand can be

either an MMX technology register, a 64-bit memory location, or an 8-bit immediate.

The PSRLW instruction shifts each of the four words of the destination operand to the right by

the number of bits specified in the count operand; the PSRLD instruction shifts each of the two

doublewords of the destination operand; and the PSRLQ instruction shifts the 64-bit quadword

in the destination operand. As the individual data elements are shifted right, the empty high-

order bit positions are filled with zeroes.

Opcode

Instruction

Description

0F D1 /r

PSRLW mm, mm/m64Shift words in mm right by amount specified in

mm/m64 while shifting in zeroes.

0F 71 /2 ib

PSRLW mm, imm8Shift words in mm right by imm8.

0F D2 /r

PSRLD mm, mm/m64Shift doublewords in mm right by amount specified

in mm/m64 while shifting in zeroes.

0F 72 /2 ib

PSRLD mm, imm8Shift doublewords in mm right by imm8.

0F D3 /r

PSRLQ mm, mm/m64Shift mm right by amount specified in mm/m64

while shifting in zeroes.

0F 73 /2 ib

PSRLQ mm, imm8Shift mm right by imm8 while shifting in zeroes.

Figure 3-79. Operation of the PSRLW Instruction

PSRLW mm, 2

mm

mm

1111111111111100

0011111111111111

0001000111000111

0000010001110001

shift right

shift right

shift right

shift right

3006027