A-12

OPCODE MAP

A.2.6.Escape Opcode Instructions

The opcode maps for the escape instruction opcodes (floating-point instruction opcodes) are

given in Table A-7 through A-22. These opcode maps are grouped by the first byte of the opcode

from D8 through DF. Each of these opcodes has a ModR/M byte. If the ModR/M byte is within

the range of 00H through BFH, bits 5, 4, and 3 of the ModR/M byte are used as an opcode ex-

tension, similar to the technique used for 1-and 2-byte opcodes (refer to Section A.2.5., Opcode

Extensions For One- And Two-byte Opcodes). If the ModR/M byte is outside the range of 00H

through BFH, the entire ModR/M byte is used as an opcode extension.

A.2.6.1.OPCODES WITH MODR/M BYTES IN THE 00H THROUGH BFH

RANGE

The opcode DD0504000000H can be interpreted as follows. The instruction encoded with this

opcode can be located in Section A.2.6.8., Escape Opcodes with DD as First Byte. Since the

ModR/M byte (05H) is within the 00H through BFH range, bits 3 through 5 (000) of this byte

indicate the opcode to be for an FLD double-real instruction (refer to Table A-9). The double-

real value to be loaded is at 00000004H, which is the 32-bit displacement that follows and be-

longs to this opcode.

A.2.6.2.OPCODES WITH MODR/M BYTES OUTSIDE THE 00H THROUGH

BFH RANGE

The opcode D8C1H illustrates an opcode with a ModR/M byte outside the range of 00H through

BFH. The instruction encoded here, can be located in Section A.2.5., Opcode Extensions For

One- And Two-byte Opcodes. In Table A-8, the ModR/M byte C1H indicates row C, column

1, which is an FADD instruction using ST(0), ST(1) as the operands.

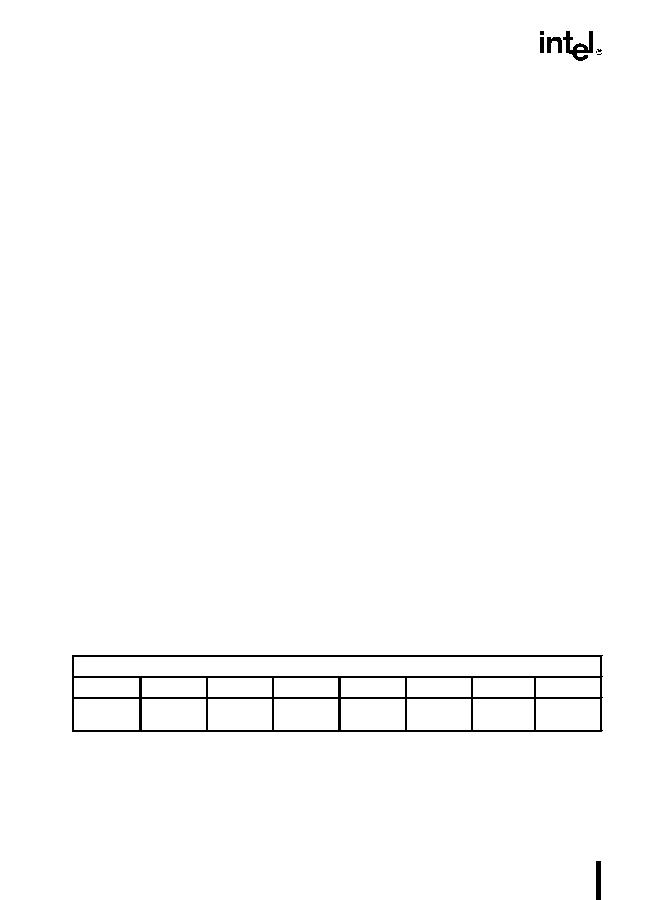

A.2.6.3.ESCAPE OPCODES WITH D8 AS FIRST BYTE

Table A-7 and A-8 contain the opcodes maps for the escape instruction opcodes that begin with

D8H. Table A-7 shows the opcode map if the accompanying ModR/M byte within the range of

00H through BFH. Here, the value of bits 5, 4, and 3 (the nnn field in Figure A-1) selects the

instruction.

Table A-7. D8 Opcode Map When ModR/M Byte is Within 00H to BFH

1

nnn Field of ModR/M Byte (refer to Figure A.2.5.)

000

001

010

011

100

101

110

111

FADD

single-real

FMUL

single-real

FCOM

single-real

FCOMP

single-real

FSUB

single-real

FSUBR

single-real

FDIV

single-real

FDIVR

single-real