B-19

INSTRUCTION FORMATS AND ENCODINGS

B.3.MMX INSTRUCTION FORMATS AND ENCODINGS

All MMX instructions, except the EMMS instruction, use the a format similar to the 2-byte

Intel Architecture integer format. Details of subfield encodings within these formats are present-

ed below. For information relating to the use of prefixes with MMX instructions, and the ef-

fects of these prefixes, see Section B.4.1. and Section 2.2., Instruction Prefixes in Chapter 2,

Instruction Format.

B.3.1.Granularity Field (gg)

The granularity field (gg) indicates the size of the packed operands that the instruction is op-

erating on. When this field is used, it is located in bits 1 and 0 of the second opcode byte. Table

B-11 shows the encoding of this gg field.

B.3.2.MMX and General-Purpose Register Fields

(mmxreg and reg)

When MMX technology registers (mmxreg) are used as operands, they are encoded in the

ModR/M byte in the reg field (bits 5, 4, and 3) and/or the R/M field (bits 2, 1, and 0). Table B-

12 shows the 3-bit encodings used for mmxreg fields.

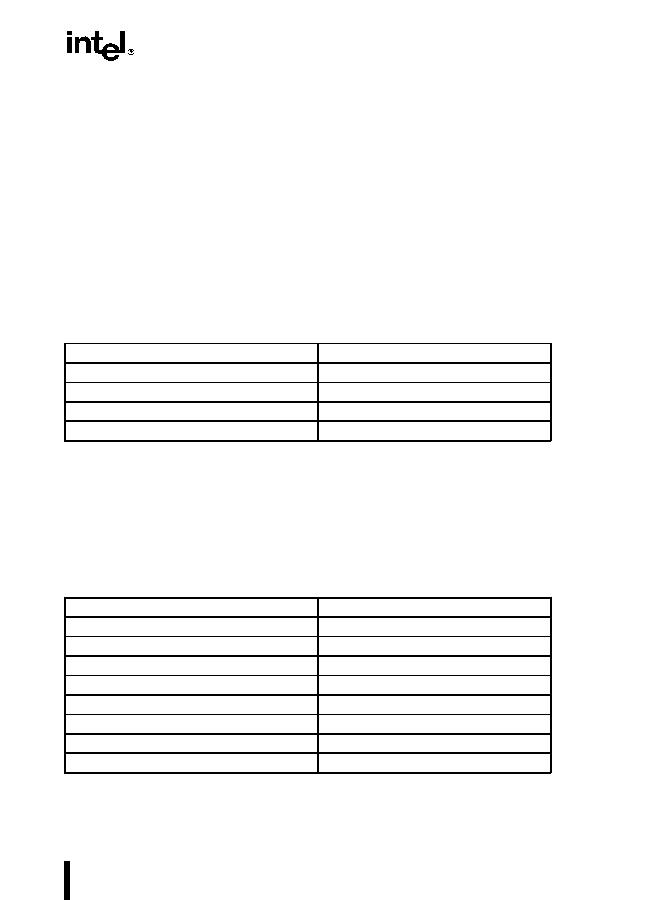

Table B-11. Encoding of Granularity of Data Field (gg)

gg

Granularity of Data

00

Packed Bytes

01

Packed Words

10

Packed Doublewords

11

Quadword

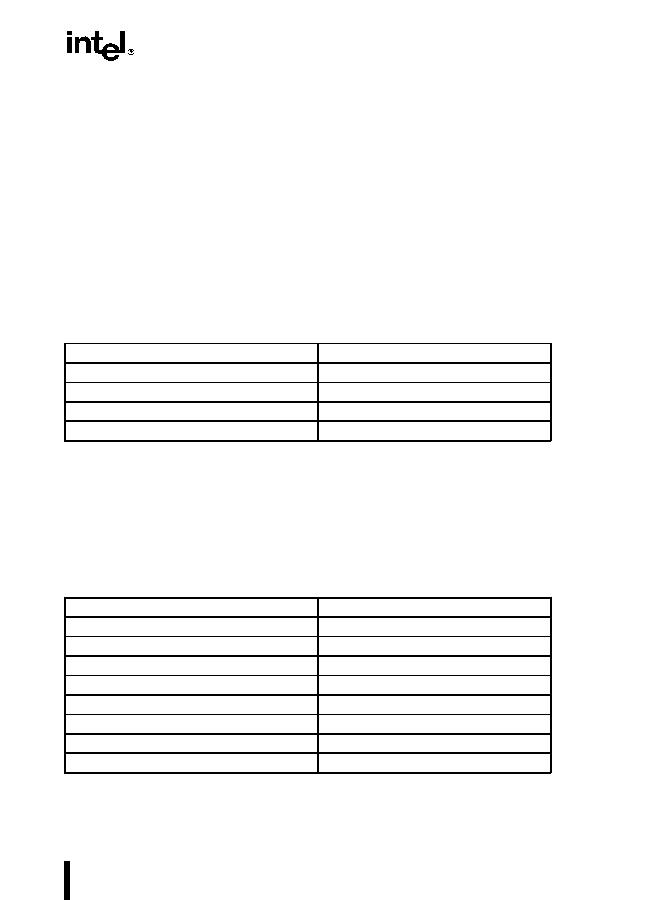

Table B-12. Encoding of the MMX Register Field (mmxreg)

mmxreg Field Encoding

MMX Register

000

MM0

001

MM1

010

MM2

011

MM3

100

MM4

101

MM5

110

MM6

111

MM7