-

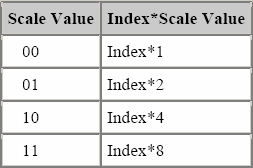

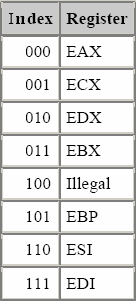

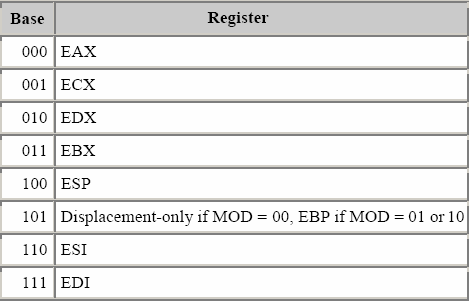

Scaled indexed addressing mode uses the second byte (namely, SIB byte) that follows the MOD-REG-R/M byte in the instruction format.

-

The MOD field still specifies the displacement size of zero, one, or four bytes.

-

The MOD-REG-R/M and SIB bytes are complex, because Intel reused 16-bit addressing circuitry in the 32-bit mode, rather than simply abandoning the 16-bit format in the 32-bit mode.

-

There are good hardware reasons for this, but the end result is a complex scheme for specifying addressing modes in the opcodes.

-

-

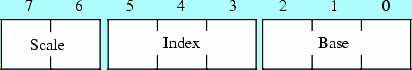

Scaled index byte layout: