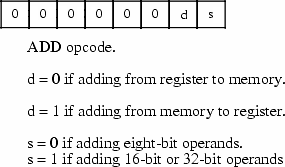

The ADD opcode can be decimal 0, 1, 2, or 3, depending on the direction and size bits in the opcode:

How could we encode various forms of the ADD instruction using different addressing modes?

| <<< Scaled Indexed Addressing Mode | Index | Encoding ADD CL, AL Instruction >>> |

The ADD opcode can be decimal 0, 1, 2, or 3, depending on the direction and size bits in the opcode:

How could we encode various forms of the ADD instruction using different addressing modes?

| <<< Scaled Indexed Addressing Mode | Index | Encoding ADD CL, AL Instruction >>> |