-

MOD-REG-R/M and SIB bytes have no bit combinations to specify an immediate operand.

-

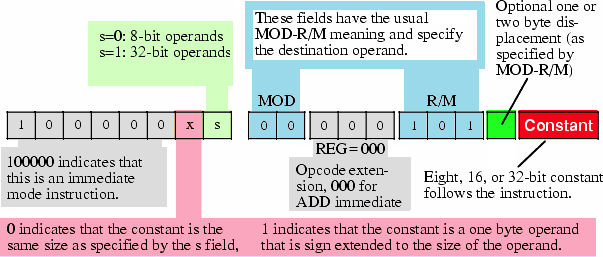

Instead, x86 uses a entirely different instruction format to specify instruction with an immediate operand.

-

There are three rules that apply:

-

Encoding x86 immediate operands: