2-10

INTRODUCTION TO THE INTEL ARCHITECTURE

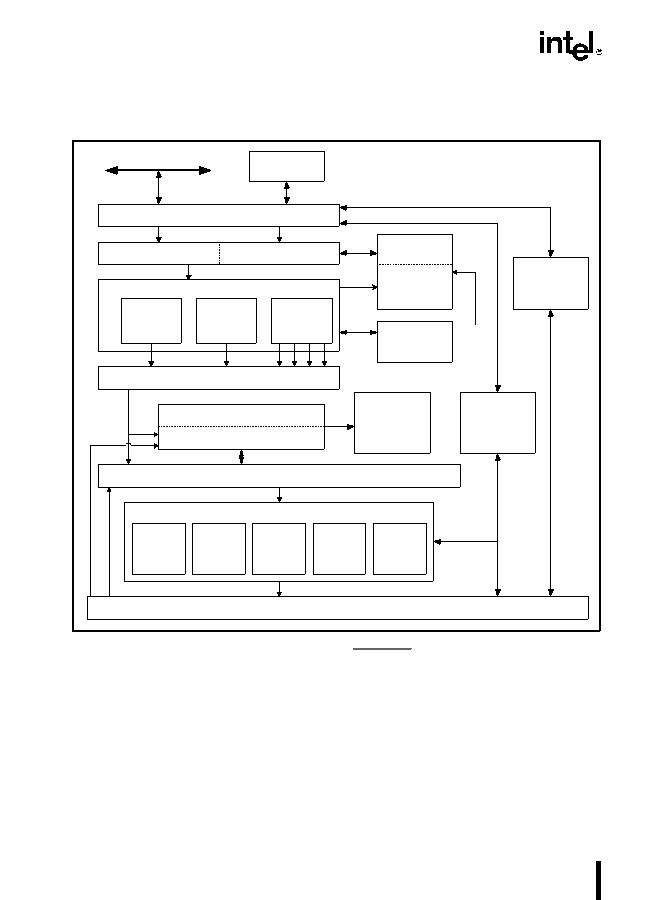

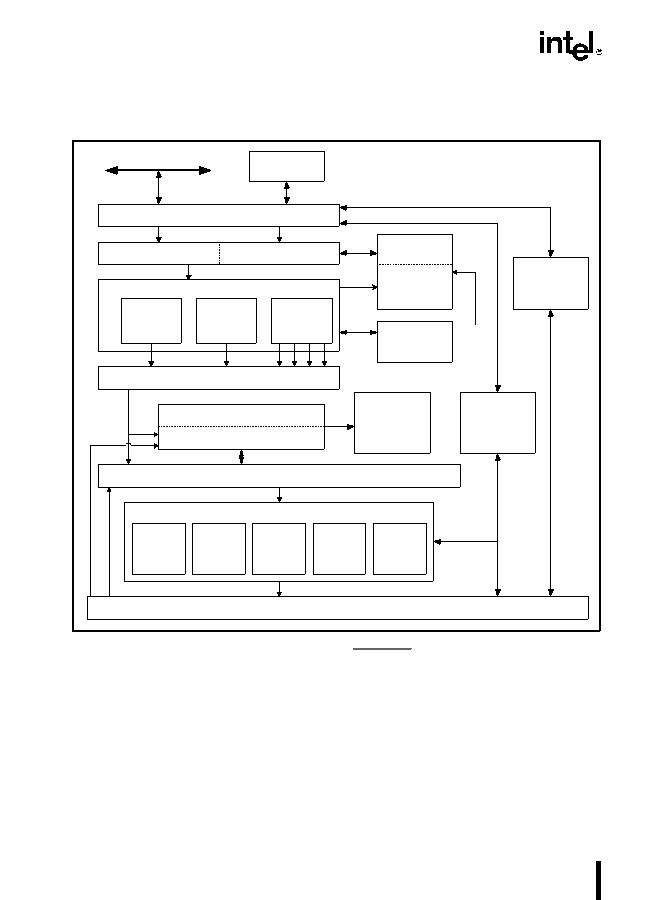

blocking. The L1 data cache automatically forwards a cache miss on to the L2 cache, and then,

if necessary, the bus interface unit forwards an L2 cache miss to system memory.

Memory requests to the L2 cache or system memory go through the memory reorder buffer,

which functions as a scheduling and dispatch station. This unit keeps track of all memory

requests and is able to reorder some requests to prevent blocks and improve throughput. For

example, the memory reorder buffer allows loads to pass stores. It also issues speculative loads.

(Stores are always dispatched in order, and speculative stores are never issued.)

Figure 2-2. Functional Block Diagram of the

P6 Family

Processor Microarchitecture

Bus Interface Unit

Simple

Instuction

Decoder

Simple

Instuction

Decoder

Complex

Instuction

Decoder

Register Alias Table

Retirement Unit

Reorder Buffer (Instruction Pool)

Reservation Station

Internal Data-Results Buses

SIMD FP

Unit

(FPU)

Floating-

Point Unit

(FPU)

Integer

Unit

Integer

Unit

Memory

Interface

Unit

Retirement

Register File

(Intel Arch.

Registers)

Data Cache

Unit (L1)

Memory

Reorder

Buffer

Microcode

Instruction

Sequencer

Next IP

Unit

Branch

Target

Buffer

L2 Cache

Instruction Decoder

Instruction Fetch UnitInstruction Cache (L1)

System Bus (External)

Cache Bus

Execution Unit

From

Integer

Unit