4-11

PROCEDURE CALLS, INTERRUPTS, AND EXCEPTIONS

Refer to Chapter 4, Protection of the Intel Architecture Software Developers Manual, Volume

3, for detailed information on calls to privileged levels and the call gate descriptor.

4.4.INTERRUPTS AND EXCEPTIONS

The processor provides two mechanisms for interrupting program execution: interrupts and

exceptions:

An interrupt is an asynchronous event that is typically triggered by an I/O device.

An exception is a synchronous event that is generated when the processor detects one or

more predefined conditions while executing an instruction. The IA specifies three classes

of exceptions: faults, traps, and aborts.

The processor responds to interrupts and exceptions in essentially the same way. When an inter-

rupt or exception is signaled, the processor halts execution of the current program or task and

switches to a handler procedure that has been written specifically to handle the interrupt or

exception condition. The processor accesses the handler procedure through an entry in the inter-

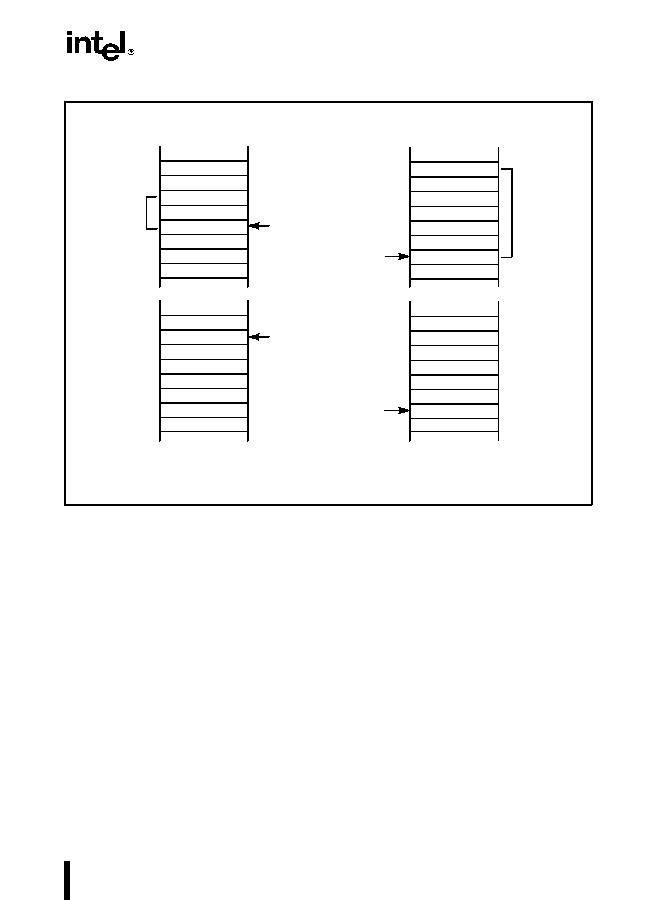

Figure 4-4. Stack Switch on a Call to a Different Privilege Level

Param 1

Param 2

ESP Before Call

Stack for

Calling Procedure

ESP After Call

Stack for

Called Procedure

Calling SS

Calling ESP

Calling CS

Param 1

Param 2

Calling EIP

Stack Frame

Before Call

Stack Frame

After Call

Param 3

Param 3

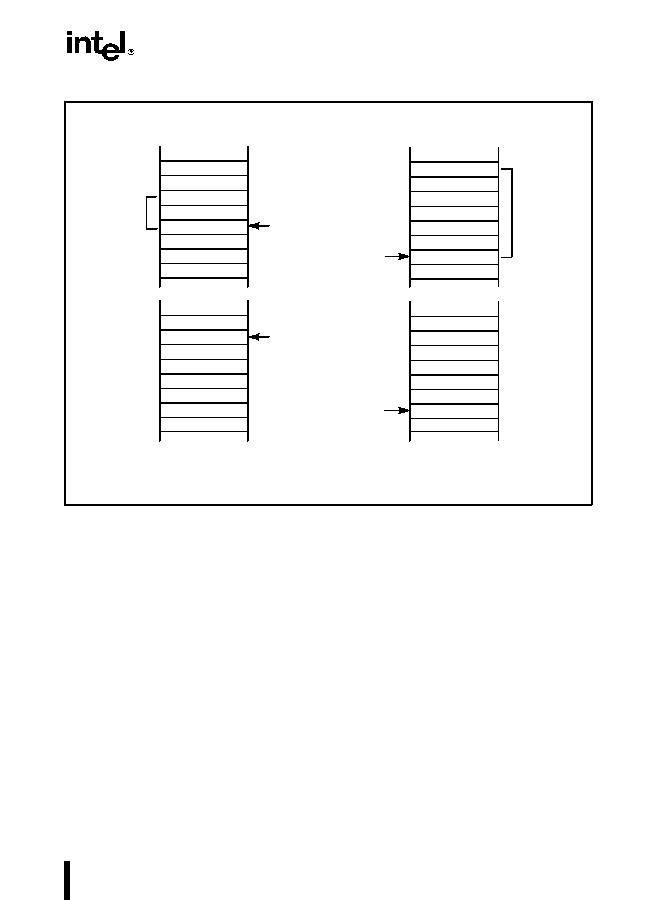

ESP After Return

ESP Before Return

Calling SS

Calling ESP

Calling CS

Param 1

Param 2

Calling EIP

Param 3

Param 1

Param 2

Param 3

Note: On a return, parameters are

released on both stacks if the

correct value is given for the n

operand in the RET n instruction.