4-14

PROCEDURE CALLS, INTERRUPTS, AND EXCEPTIONS

1. The UD2 instruction was introduced in the Pentium

®

Pro processor.

2. IA processors after the Intel386 processor do not generate this exception.

3. This exception was introduced in the Intel486 processor.

4. This exception was introduced in the Pentium

®

processor and enhanced in the Pentium

®

Pro processor.

5. This exception was introduced in the Pentium

®

III processor.

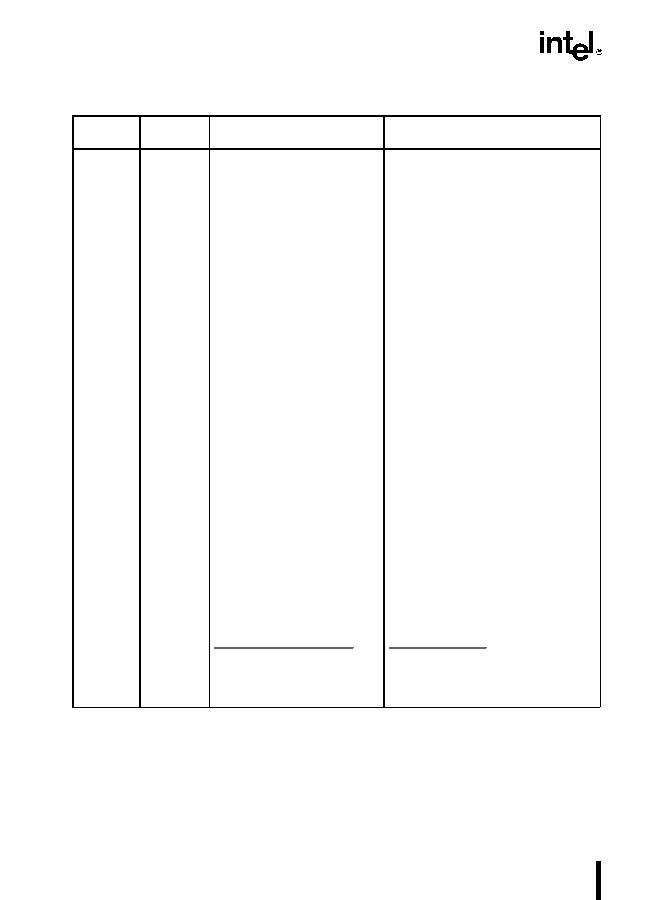

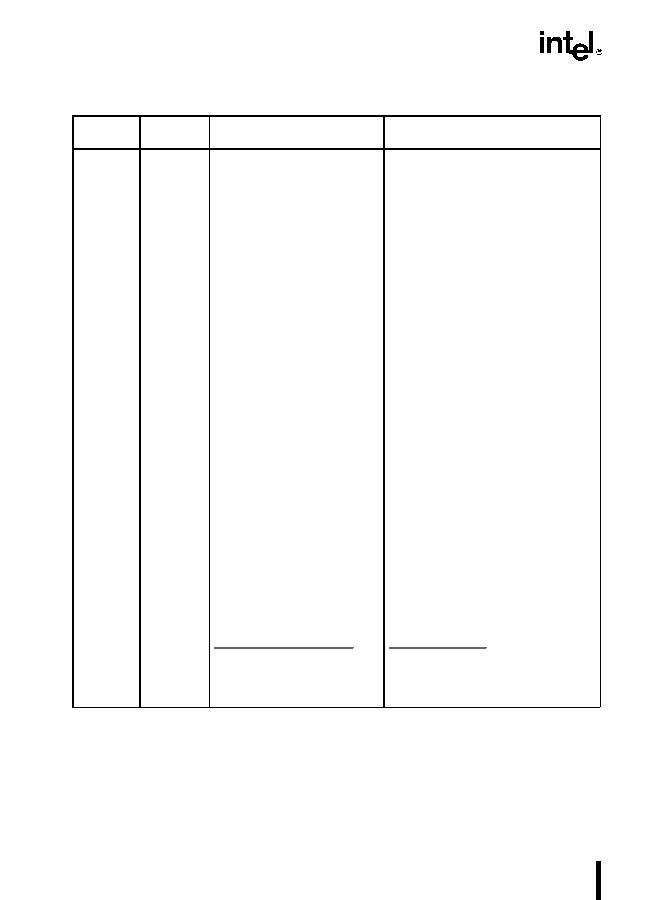

Table 4-1. Exceptions and Interrupts

Vector No.Mnemonic

Description

Source

0

#DEDivide Error

DIV and IDIV instructions.

1

#DBDebug

Any code or data reference.

2

NMI Interrupt

Non-maskable external interrupt.

3

#BPBreakpoint

INT 3 instruction.

4

#OFOverflow

INTO instruction.

5

#BRBOUND Range Exceeded

BOUND instruction.

6

#UDInvalid Opcode (UnDefined

Opcode)

UD2 instruction or reserved opcode.

1

7

#NMDevice Not Available (No Math

Coprocessor)

Floating-point or WAIT/FWAIT instruction.

8

#DFDouble Fault

Any instruction that can generate an

exception, an NMI, or an INTR.

9

CoProcessor Segment Overrun

(reserved)

Floating-point instruction.

2

10

#TSInvalid TSS

Task switch or TSS access.

11

#NPSegment Not Present

Loading segment registers or accessing

system segments.

12

#SSStack Segment Fault

Stack operations and SS register loads.

13

#GPGeneral Protection

Any memory reference and other

protection checks.

14

#PFPage Fault

Any memory reference.

15

(Intel reserved. Do not use.)

16

#MFFloating-Point Error (Math Fault)Floating-point or WAIT/FWAIT instruction.

17

#ACAlignment Check

Any data reference in memory.

3

18

#MCMachine Check

Error codes (if any) and source are model

dependent.

4

19

#XF

Streaming SIMD Extensions

SIMD floating-point

numeric exceptions.

5

20-31

(Intel reserved. Do not use.)

32-255

Maskable Interrupts

External interrupt from INTR pin or INT n

instruction.