7-19

FLOATING-POINT UNIT

For example, the following value (a) has a 24-bit fraction. The least-significant bit of this frac-

tion (the underlined bit) cannot be encoded exactly in the single-real format (which has only a

23-bit fraction):

(a) 1.0001 0000 1000 0011 1001 0111

E

2

101

To round this result (a), the FPU first selects two representable fractions b and c that most

closely bracket a in value (b < a < c).

(b) 1.0001 0000 1000 0011 1001 011E

2

101

(c) 1.0001 0000 1000 0011 1001 100E

2

101

The FPU then sets the result to b or to c according to the rounding mode selected in the RC field.

Rounding introduces an error in a result that is less than one unit in the last place to which the

result is rounded.

The rounded result is called the inexact result. When the FPU produces an inexact result, the

floating-point precision (inexact) flag (PE) is set in the FPU status word.

When the overflow exception is masked and the infinitely precise result is between the largest

positive finite value allowed in a particular format and

+?

, the FPU rounds the result as shown

in Table 7-6.

When the overflow exception is masked and the infinitely precise result is between the largest

negative finite value allowed in a particular format and

??

, the FPU rounds the result as shown

in Table 7-7.

The rounding modes have no effect on comparison operations, operations that produce exact

results, or operations that produce NaN results.

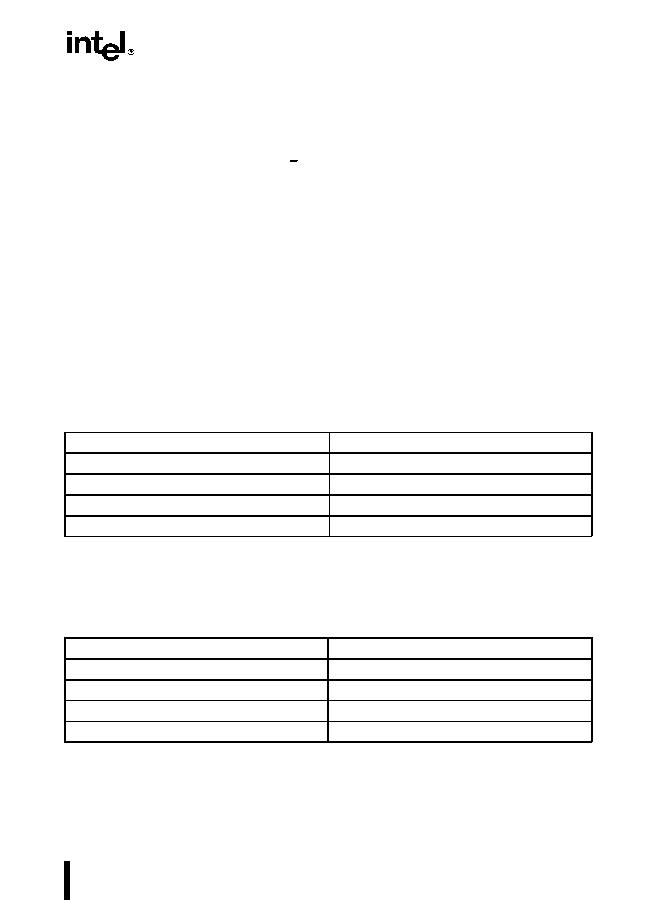

Table 7-6. Rounding of Positive Numbers with Masked Overflow

Rounding Mode

Result

Rounding to nearest (even)

+

?

Rounding toward zero (Truncate)

Maximum, positive finite value

Rounding up (toward

+?

)

+

?

Rounding down) (toward

??

)

Maximum, positive finite value

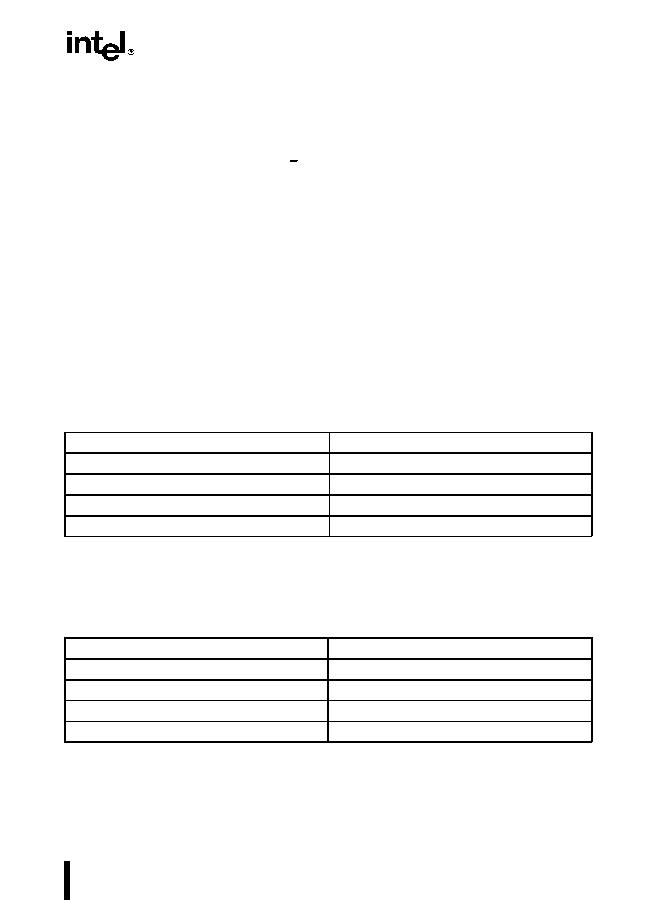

Table 7-7. Rounding of Negative Numbers with Masked Overflow

Rounding Mode

Result

Rounding to nearest (even)

??

Rounding toward zero (Truncate)

Maximum, negative finite value

Rounding up (toward

+?

)

Maximum, negative finite value

Rounding down) (toward

??

)

??