7-32

FLOATING-POINT UNIT

Refer to Section 6.2.3., Floating-Point Instructions in Chapter 6, Instruction Set Summary, for

a list of the floating-point instructions by category.

The following section briefly describes the instructions in each category. Detailed descriptions

of the floating-point instructions are given in Chapter 3, Instruction Set Reference, in the Intel

Architecture Software Developers Manual, Volume 2.

7.5.1.Escape (ESC) Instructions

All of the instructions in the FPU instruction set fall into a class of instructions known as escape

(ESC) instructions. All of these instructions have a common opcode format, which is slightly

different from the format used by the integer and operating-system instructions.

7.5.2.FPU Instruction Operands

Most floating-point instructions require one or two operands, located on the FPU data-register

stack or in memory. (None of the floating-point instructions accept immediate operands.)

When an operand is located in a data register, it is referenced relative to the ST(0) register (the

register at the top of the register stack), rather than by a physical register number. Often the

ST(0) register is an implied operand.

Operands in memory can be referenced using the same operand addressing methods available

for the integer and system instructions.

7.5.3.Data Transfer Instructions

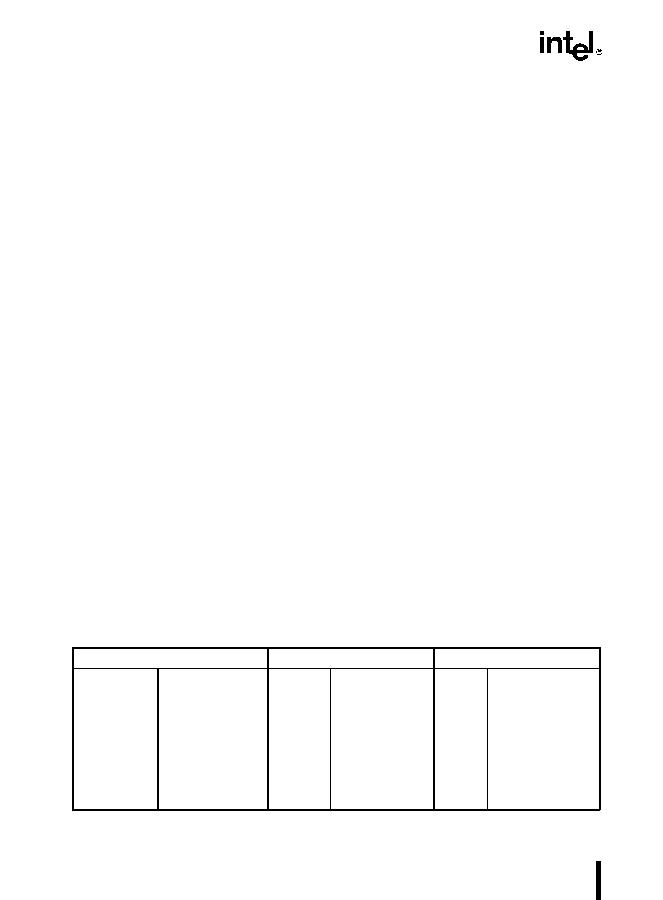

The data transfer instructions (refer to Table 7-13) perform the following operations:

Load real, integer, or packed BCD operands from memory into the ST(0) register.

Store the value in the ST(0) register in memory in real, integer, or packed BCD format.

Move values between registers in the FPU register stack.

Table 7-13. Data Transfer Instructions

Real

Integer

Packed Decimal

FLD

Load Real

FILDLoad IntegerFBLDLoad Packed

Decimal

FST

Store Real

FISTStore Integer

FSTP

Store Real and

Pop

FISTPStore Integer

and Pop

FBSTPStore Packed

Decimal and Pop

FXCH

Exchange Register

Contents

FCMOVccConditional Move