8-11

PROGRAMMING WITH THE INTEL MMX TECHNOLOGY

8.4.COMPATIBILITY WITH FPU ARCHITECTURE

The MMX state is aliased upon the IA floating-point state. No new state or mode is added to

support the MMX technology. The same floating-point instructions that save and restore the

floating-point state also handle the MMX state (for example, during context switching).

MMX technology uses the same interface techniques between the floating-point architecture

and the operating system (primarily for task switching purposes). For more details, refer to

Chapter 10, MMX Technology System Programming, in the Intel Architecture Software Devel-

opers Manual, Volume 3.

8.4.1.MMX Instructions and the Floating-Point Tag Word

After each MMX instruction, the entire floating-point tag word is set to Valid (00s). The

Empty MMX state (EMMS) instruction sets the entire floating-point tag word to Empty (11s).

Chapter 10, MMX Technology System Programming, in the Intel Architecture Software Devel-

opers Manual, Volume 3, describes the effects of floating-point and MMX instructions on the

floating-point tag word. For details on floating-point tag word, refer to Section 7.3.6., FPU Tag

Word in Chapter 7, Floating-Point Unit.

8.4.2.Effect of Instruction Prefixes on MMX Instructions

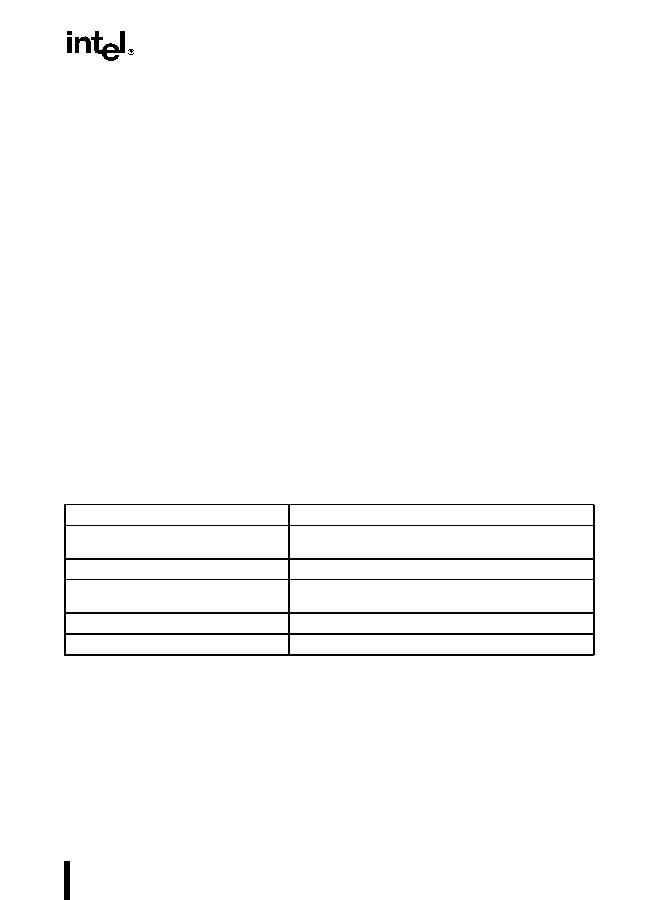

Table 8-3 details the effect of an instruction prefix on an MMX instruction.

Refer to Section 2.2., Instruction Prefixes in Chapter 2, Instruction Format of the Intel Archi-

tecture Software Developers Manual, Volume 2, for detailed information on prefixes.

8.5.WRITING APPLICATIONS WITH MMX CODE

The following sections give guidelines for writing applications code using the MMX tech-

nology.

Table 8-3. Effect of Prefixes on MMX Instructions

Prefix Type

Effect of Prefix

Address size (67H)

Affects MMX instructions with a memory operand.

Ignored by MMX instructions without a memory operand.

Operand size (66H)

Reserved.

Segment override

Affects MMX instructions with a memory operand.

Ignored by MMX instructions without a memory operand.

Repeat

Reserved.

Lock (F0H)

Generates an invalid opcode exception.