11-5

PROCESSOR IDENTIFICATION AND FEATURE DETERMINATION

11.3.CPUID INSTRUCTION EXTENSIONS

The CPUID instructions of all P6-family processors behave identically. The CPUID instruction

is described in detail in the application note, AP-485, Intel Processor Identification and the

CPUID Instruction. This section describes processor-specific information returned by the

CPUID instruction.

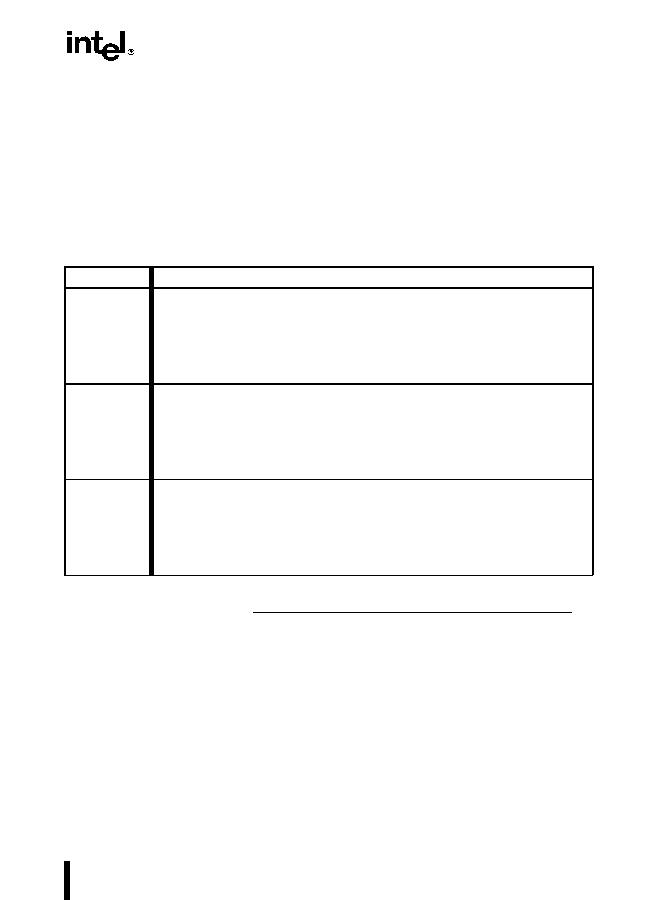

The CPUID instructions behavior varies depending upon the contents of the EAX register when

the instruction is executed. Table 11-1 shows the interaction between the value in EAX before

the call to CPUID and the value that CPUID returns.

Refer to the CPUID application note, AP-485, for details on cache information. AP-485 is avail-

able from the following web site: http://developer.intel.com/design/pro/applnots/ap485.htm

.

In addition, the following two new cache descriptors are defined for P6-family processors with

Model > 3:

1M L2 Cache4-way set associative32-byte line size44h

2M L2 Cache4-way set associative32-byte line size45h

11.3.1.Version Information

When the CPUID instruction is executed with a 1 in EAX, it returns version and feature infor-

mation. Figure 11-1 shows the version information bit fields returned by CPUID in EAX. The

233, 266, and 300 MHz Pentium

®

II processors are indicated by a 6 in the Family ID and a

Table 11-1. EAX Input Value and CPUID Return Values

EAX

CPUID Return Values

0

EAX

EBX

ECX

EDX

Maximum CPUID input value

756E6547H

uneG (G in BL)

6C65746EH

letn (n in CL)

49656E69H

leni (i in DL)

1

EAX

EBX

ECX

EDX

Version information (Type, Family, Model, Stepping)

Reserved

Reserved

Feature Information

2

EAX

EBX

ECX

EDX

Cache Information

Cache Information

Cache Information

Cache Information