11-7

PROCESSOR IDENTIFICATION AND FEATURE DETERMINATION

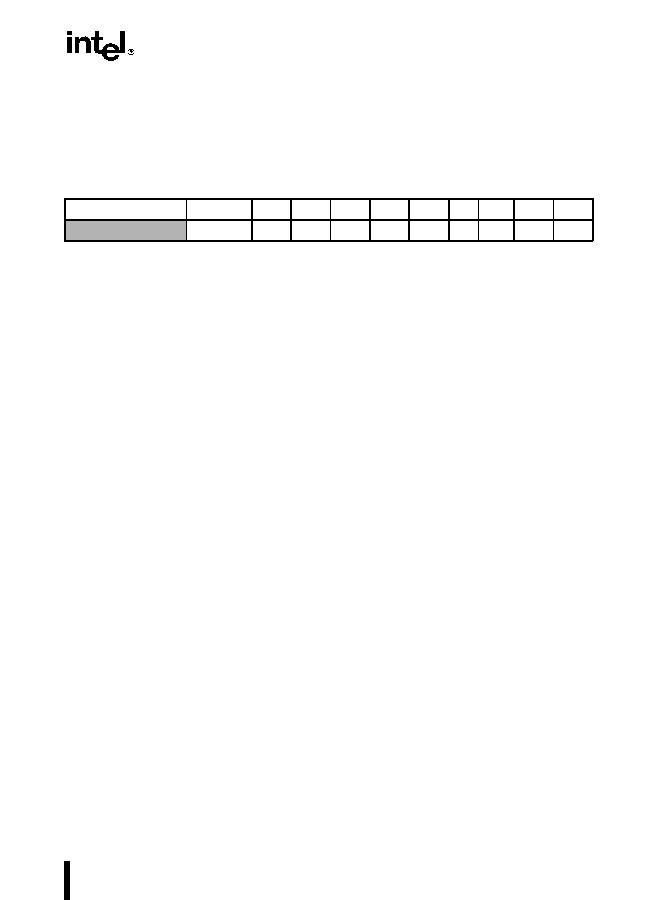

11.3.2.Control Register Extensions

The control registers (CR0, CR1, CR2, CR3, and CR4) determine the operating mode of the

processor and the characteristics of the currently executing task. A new field has been added to

CR4, which contains a group of flags used to enable several architectural extensions as depicted

in Figure 11-3.

The new field at bit 9 (OSFXSR) is set by the operating system to indicate that it uses the

FXSAVE/FXRSTOR instructions for saving/restoring FP/MMX state during context

switches. This bit defaults to clear (zero) at processor initialization.

31

1009080706050403020100

Reserved (set to 0)OSFXSRPCEPGEMCEPAEPSEDETSDPVIVME

Figure 11-3. CR4 Register Extensions