F-10

GUIDELINES FOR WRITING SIMD FLOATING-POINT EXCEPTION

F.4.2.3.CONDITION CODES, EXCEPTION FLAGS, AND RESPONSE FOR

MASKED AND UNMASKED NUMERIC EXCEPTIONS

In the following, the masked response is what the processor provides when a masked exception

is raised by a Streaming SIMD Extensions numeric instruction. The same response is provided

by the floating-point emulator for Streaming SIMD Extensions numeric instructions, when cer-

tain components of the quadruple input operands generate exceptions that are masked (the em-

ulator also generates the correct answer, as specified by the IEEE standard wherever applicable,

in the case when no floating-point exception occurs). The unmasked response is what the emu-

lator provides to the user handler for those components of the quadruple input operands of the

Streaming SIMD Extensions instructions that raise unmasked exceptions. Note that for pre-

computation exceptions (floating-point faults), no result is provided to the user handler. For

post-computation exceptions (floating-point traps), a result is also provided to the user handler,

as specified below.

In the following tables, the result is denoted by res, with the understanding that for the actual

instruction, the destination coincides with the first source operand (except for COMISS and

UCOMISS, whose destination is the EFLAGS register).

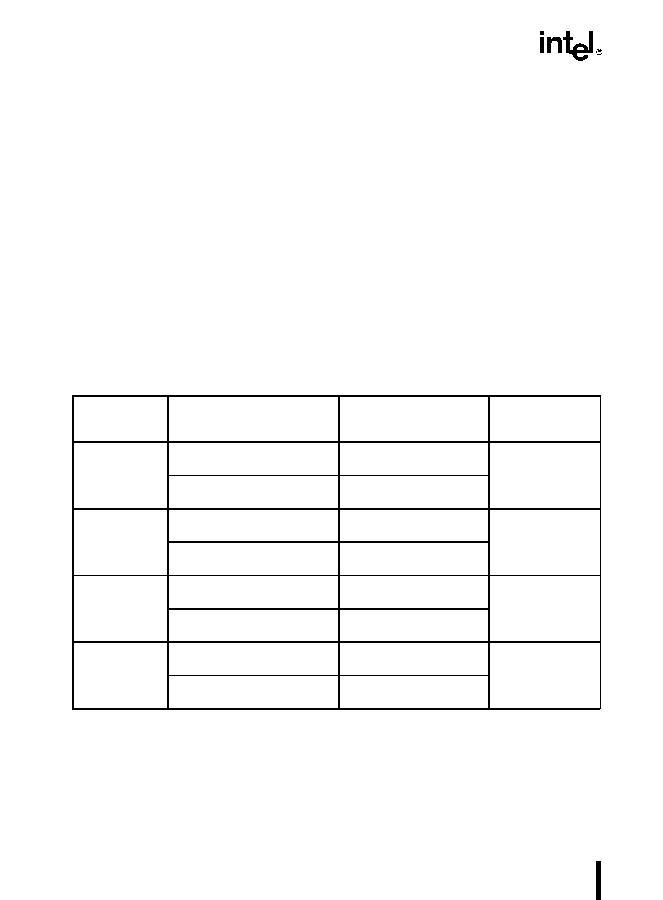

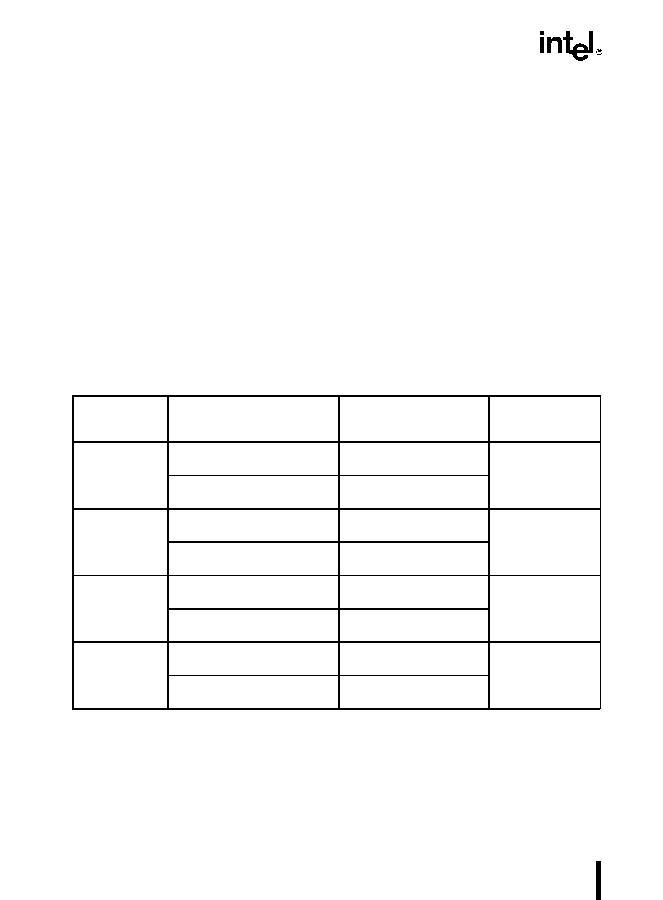

Table F-11. #I - Invalid Operations

Instruction

Condition

Masked Response

Unmasked

Response and

Exception Code

ADDPS

src1 or src2 = SNaN

Refer to Table F-1 for NaN

operands, #IA=1

src1, src2

unchanged, #IA=1

ADDSS

src1=+Inf, src2 = -Inf or

src1=-Inf, src2 = +Inf

res = QNaN Indefinite,

#IA=1

SUBPS

src1 or src2 = SNaN

Refer to Table F-1 for NaN

operands, #IA=1

src1, src2

unchanged, #IA=1

SUBSS

src1=+Inf, src2 = +Inf or

src1=-Inf, src2 = -Inf

res = QNaN Indefinite,

#IA=1

MULPS

src1 or src2 = SNaN

Refer to Table F-1 for NaN

operands, #IA=1

src1, src2

unchanged, #IA=1

MULSS

src1=±Inf, src2 = ±0 or

src1=±0, src2 = ±Inf

res = QNaN Indefinite,

#IA=1

DIVPS

src1 or src2 = SNaN

Refer to Table F-1 for NaN

operands, #IA=1

src1, src2

unchanged, #IA=1

DIVSS

src1=±Inf, src2 = ±Inf or

src1=±0, src2 = ±0

res = QNaN Indefinite,

#IA=1