F-13

GUIDELINES FOR WRITING SIMD FLOATING-POINT EXCEPTION

F.4.3.SIMD Floating-Point Emulation Implementation Example

The sample code listed below may be considered as being part of a user-level floating-point ex-

ception filter for Streaming SIMD Extensions numeric instructions. It is assumed that the filter

function is invoked by a low-level exception handler (reached via interrupt vector 19 when an

unmasked floating-point exception occurs), and that it operates as explained in Section F.4.1.,

Floating-Point Emulation The sample code does the emulation for the add, subtract, multiply,

and divide operations. For this, it uses C code and IA-32 FPU operations (readability, and not

efficiency was the primary goal). Operations corresponding to other Streaming SIMD Exten-

sions numeric instructions have to be emulated, but only place holders for them are included.

The example assumes that the emulation function receives a pointer to a data structure specify-

ing a number of input parameters: the operation that caused the exception, a set of two sub-op-

erands (unpacked, of type float), the rounding mode (the precision is always single), exception

masks (having the same relative bit positions as in the MXCSR but starting from bit 0 in an un-

signed integer), and a flush-to-zero indicator. The output parameters are a floating-point result

(of type float), the cause of the exception (identified by constants not explicitly defined below),

and the exception status flags. The corresponding C definition is:

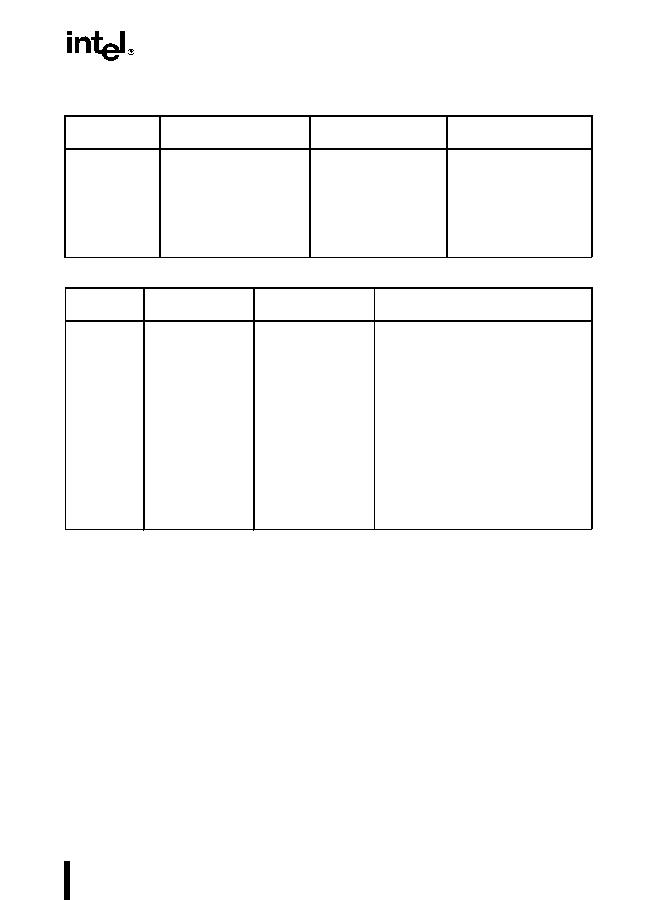

Table F-15. #U - Numeric Underflow

Instruction

Condition

Masked ResponseUnmasked Response

and Exception Code

ADDPS

SUBPS

MULPS

DIVPS

ADDSS

SUBSS

MULSS

DIVSS

result calculated with

unbounded exponent and

rounded to the destination

precision < smallest single-

precision finite normal value

#UE=1 and #PE=1,

but only if the result is

exact

res = ±0, denormal, or

normal

res = (result calculated with

unbounded exponent and

rounded to the destination

precision) * 2

192

#UE=1

#PE=1 if the result is

inexact

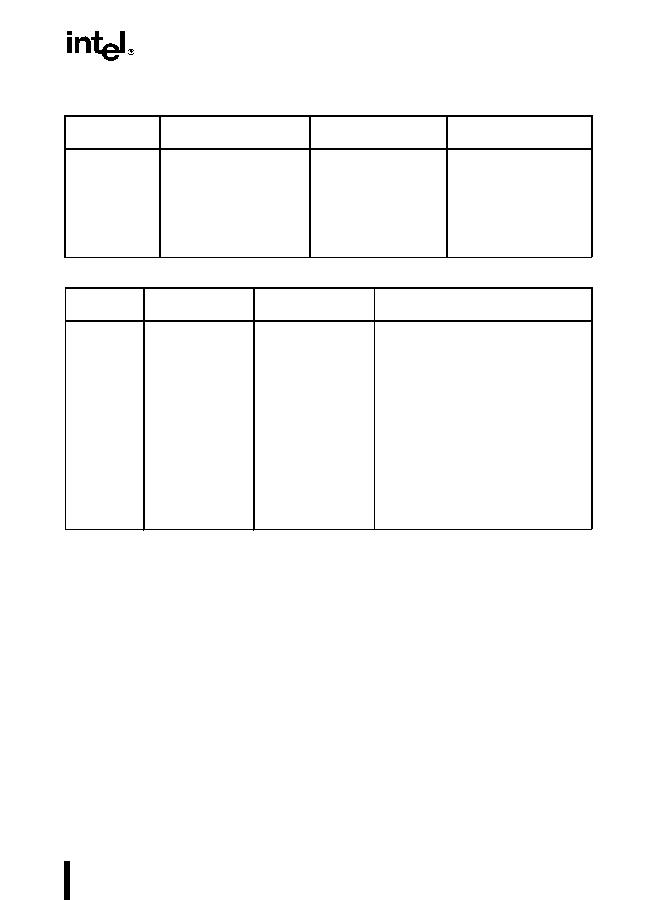

Table F-16. #P - Inexact Result (Precision)

InstructionConditionMasked ResponseUnmasked Response and Exception

Code

ADDPS

SUBPS

MULPS

DIVPS

SQRTPS

CVTPI2PS

CVTPS2PI

CVTTPS2PI

ADDSS

SUBSS

MULSS

DIVSS

SQRTSS

CVTSI2SS

CVTSS2SI

CVTTSS2SI

the result is not

exactly

representable in the

destination format

res = result rounded

to the destination

precision and using

the bounded

exponent, but only if

no unmasked

underflow or overflow

conditions occur (This

exception can occur

in the presence of a

masked underflow or

overflow)

#PE=1

only if no underflow/overflow condition

occurred, or if the corresponding

exceptions are masked:

set #OE if masked overflow and set result

as described above for masked overflow;

set #UE if masked underflow and set

result as described above for masked

underflow;

if neither underflow nor overflow, res = the

result rounded to the destination precision

and using the bounded exponent

set #PE=1