2-1

CHAPTER 2

INSTRUCTION FORMAT

This chapter describes the instruction format for all Intel Architecture processors.

2.1.GENERAL INSTRUCTION FORMAT

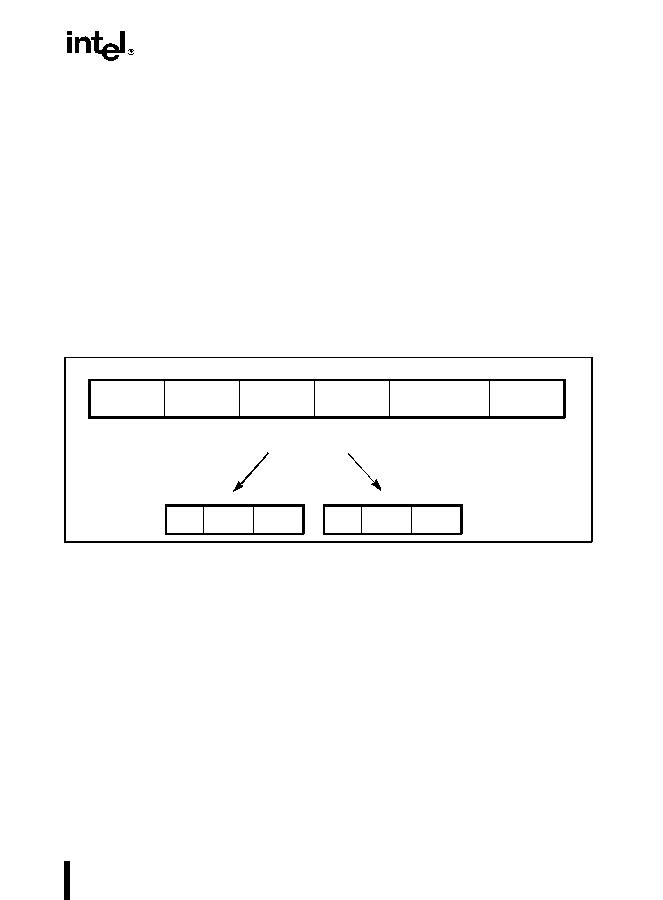

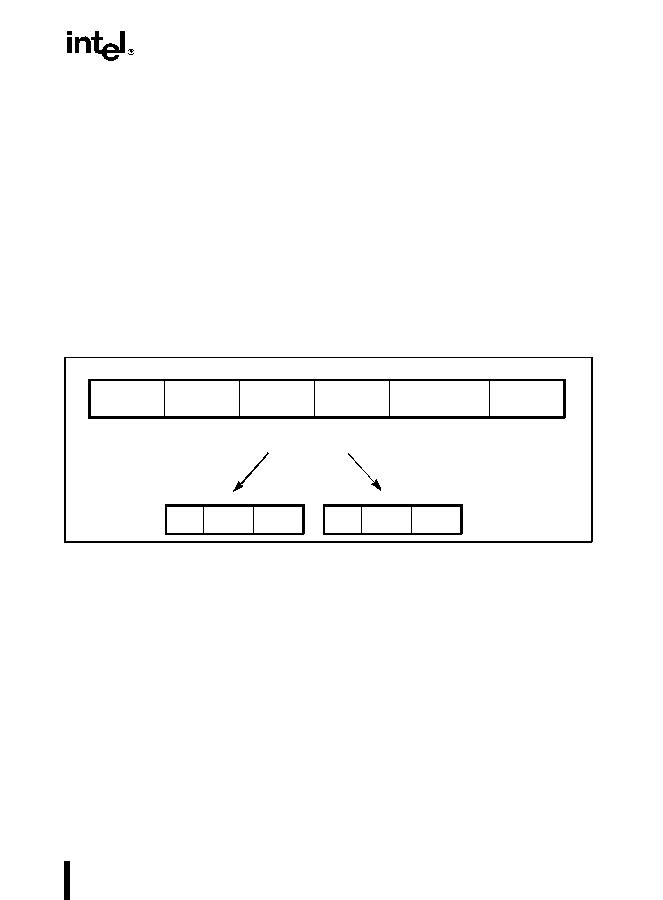

All Intel Architecture instruction encodings are subsets of the general instruction format shown

in Figure 2-1. Instructions consist of optional instruction prefixes (in any order), one or two

primary opcode bytes, an addressing-form specifier (if required) consisting of the ModR/M byte

and sometimes the SIB (Scale-Index-Base) byte, a displacement (if required), and an immediate

data field (if required).

2.2.INSTRUCTION PREFIXES

The instruction prefixes are divided into four groups, each with a set of allowable prefix codes:

Lock and repeat prefixes.

F0HLOCK prefix.

F2HREPNE/REPNZ prefix (used only with string instructions).

F3HREP prefix (used only with string instructions).

F3HREPE/REPZ prefix (used only with string instructions).

F3HStreaming SIMD Extensions prefix.

Figure 2-1. Intel Architecture Instruction Format

Instruction

PrefixesOpcodeModR/M

SIB

DisplacementImmediate

Mod

R/M

Reg/

Opcode

0

2

7653

Scale

Base

0

2

7653

Index

Immediate

data of

1, 2, or 4

bytes or none

Address

displacement

of 1, 2, or 4

bytes or none

1 byte

(if required)

1 byte

(if required)

1 or 2 byte

opcode

Up to four

prefixes of

1-byte each

(optional)