3-14

INSTRUCTION SET REFERENCE

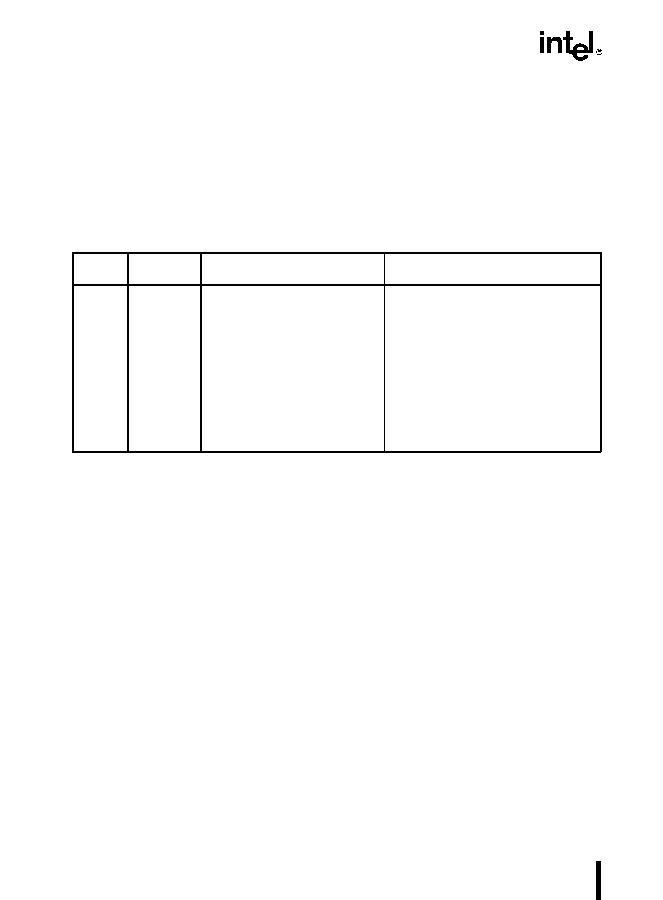

3.1.9.Floating-Point Exceptions

The Floating-Point Exceptions section lists additional exceptions that can occur when a

floating-point instruction is executed in any mode. All of these exception conditions result in a

floating-point error exception (#MF, vector number 16) being generated. Table 3-3 associates

each one- or two-letter mnemonic with the corresponding exception name. Refer to Section 7.8.,

Floating-Point Exception Conditions in Chapter 7, Floating-Point Unit of the Intel Architecture

Software Developers Manual, Volume 1, for a detailed description of these exceptions.

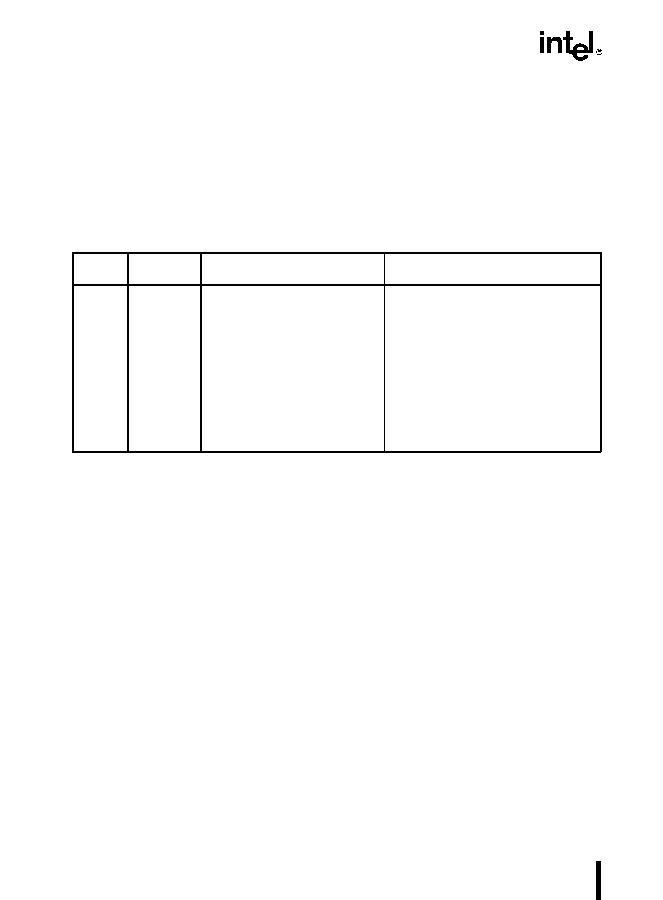

3.1.10.SIMD Floating-Point Exceptions - Streaming SIMD

Extensions Only

The SIMD Floating-Point Exceptions section lists additional exceptions that can occur when

a SIMD floating-point instruction is executed in any mode. All of these exception conditions

result in a SIMD floating-point error exception (#XF, vector number 19) being generated. Table

3-4 associates each one-or two-letter mnemonic with the corresponding exception name. For a

detailed description of these exceptions, refer to Chapter 9, Programming with the Streaming

SIMD Extensions, of the Intel Architecture Software Developers Manual, Volume 1.

Table 3-3. Floating-Point Exception Mnemonics and Names

Vector

No.Mnemonic

Name

Source

16

#IS

#IA

Floating-point invalid operation:

- Stack overflow or underflow

- Invalid arithmetic operation

- FPU stack overflow or underflow

- Invalid FPU arithmetic operation

16

#ZFloating-point divide-by-zeroFPU divide-by-zero

16

#DFloating-point denormalized

operation

Attempting to operate on a denormal

number

16

#OFloating-point numeric overflowFPU numeric overflow

16

#UFloating-point numeric underflowFPU numeric underflow

16

#PFloating-point inexact result

(precision)

Inexact result (precision)