3-15

INSTRUCTION SET REFERENCE

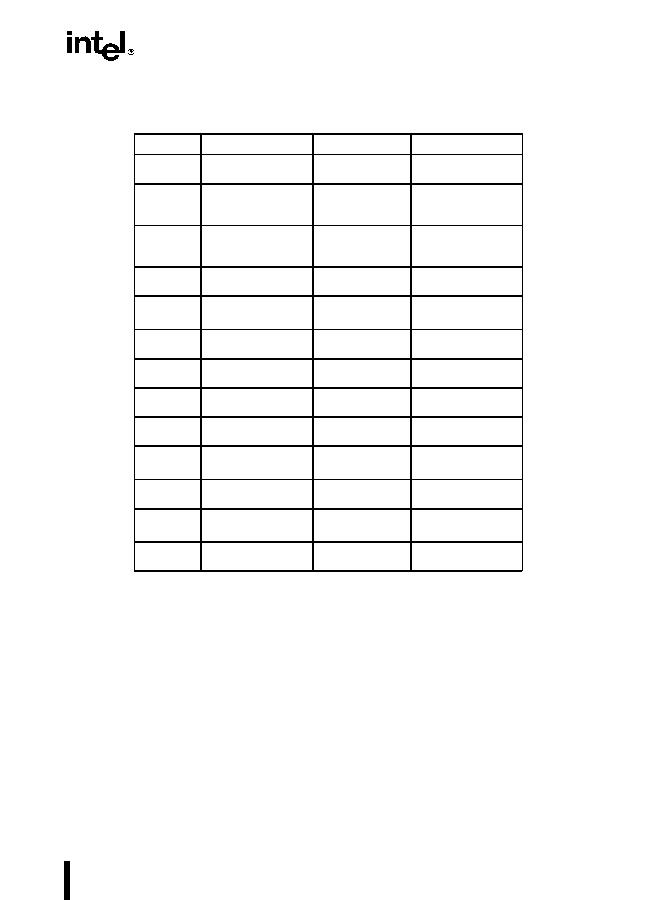

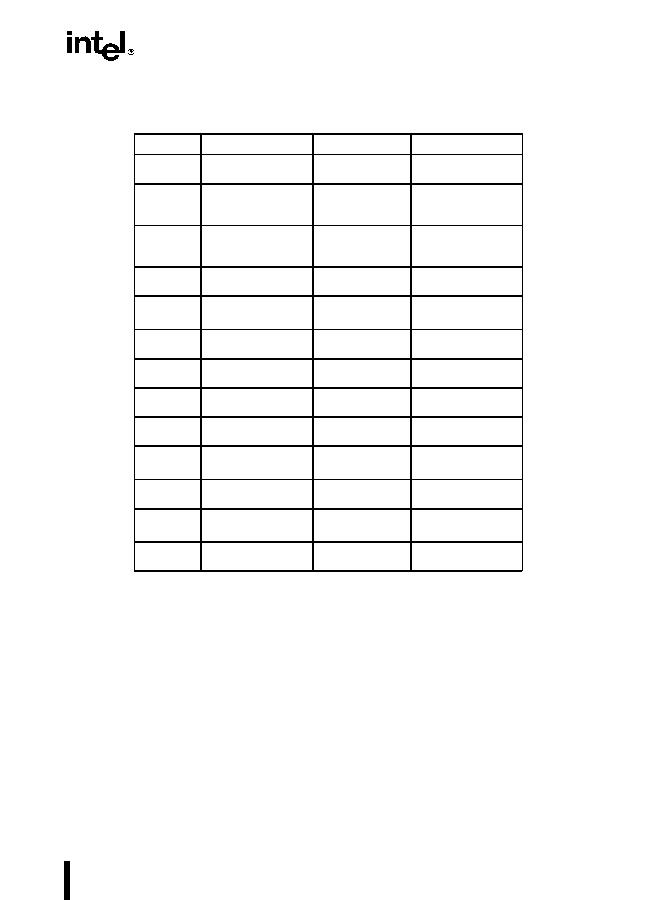

Table 3-4. SIMD Floating-Point Exception Mnemonics and Names

Note 1:These are system exceptions. Table 3-5 lists the causes for Interrupt 6 and Interrupt 7 with Stream-

ing SIMD Extensions.

Note 2:Executing a Streaming SIMD Extension with a misaligned 128-bit memory reference generates a

general protection exception; a 128-bit reference within the stack segment, which is not aligned to a 16-

byte boundary will also generate a GP fault, not a stack exception (SS). However, the MOVUPS instruc-

tion, which performs an unaligned 128-bit load or store, will not generate an exception for data that is not

aligned to a 16-byte boundary.

Note 3:This type of alignment check is done for operands which are less than 128-bits in size: 32-bit scalar

single and 16-bit/32-bit/64-bit integer MMX technology; the exception is the MOVUPS instruction,

which performs a 128-bit unaligned load or store, is also covered by this alignment check. There are

three conditions that must be true to enable #AC interrupt generation.

Note 4:Invalid, Divide-by-zero and Denormal exceptions are pre-computation exceptions, i.e., they are

detected before any arithmetic operation occurs.

Note 5:Underflow, Overflow and Precision exceptions are post-computation exceptions.

Vector No.Mnemonic

Name

Source

6

#UD

Invalid opcodeMemory access

6

#UD

Invalid opcodeRefer to Note 1 &

Table 3-5

7

#NM

Device not

availableRefer to Note 1 &

Table 3-5

12

#SS

Stack exceptionMemory access

13

#GP

General

protectionRefer to Note 2

14

#PF

Page faultMemory access

17

#AC

Alignment checkRefer to Note 3

19

#I

Invalid operationRefer to Note 4

19

#Z

Divide-by-zeroRefer to Note 4

19

#D

Denormalized

operand

Refer to Note 4

19

#O

Numeric overflowRefer to Note 5

19

#U

Numeric

underflow

Refer to Note 5

19

#P

Inexact resultRefer to Note 5