3-86

INSTRUCTION SET REFERENCE

CMPPSPacked Single-FP Compare (Continued)

Virtual Mode Exceptions

Same exceptions as in Real Address Mode.

#PF(fault-code)For a page fault.

Comments

Compilers and assemblers should implement the following 2-operand pseudo-ops in addition to

the 3-operand CMPPS instruction:

The greater-than relations not implemented in hardware require more than one instruction to

emulate in software and therefore should not be implemented as pseudo-ops. (For these, the

programmer should reverse the operands of the corresponding less than relations and use move

instructions to ensure that the mask is moved to the correct destination register and that the

source operand is left intact.)

Bits 7-4 of the immediate field are reserved. Different processors may handle them differently.

Usage of these bits risks incompatibility with future processors.

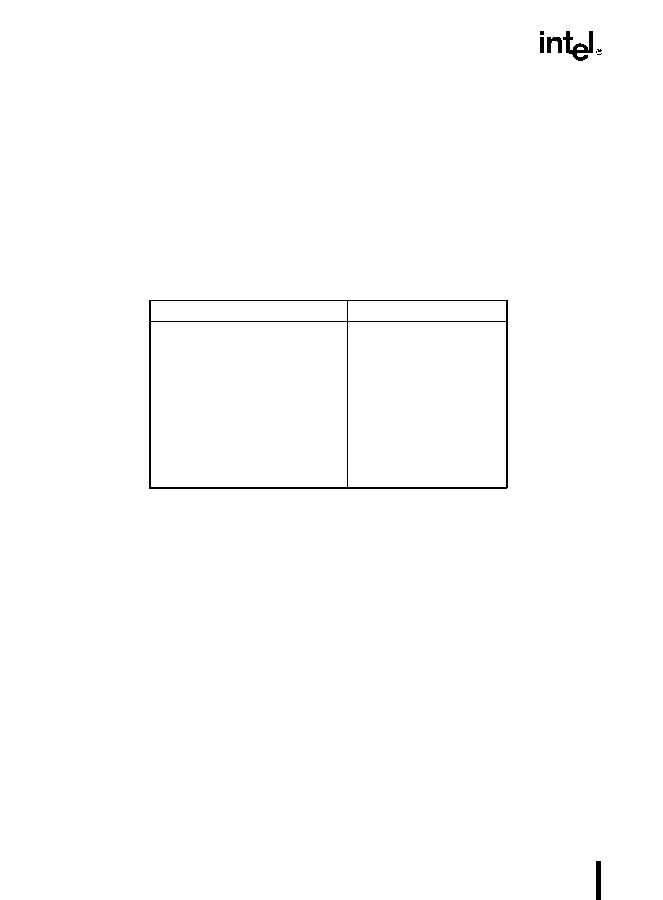

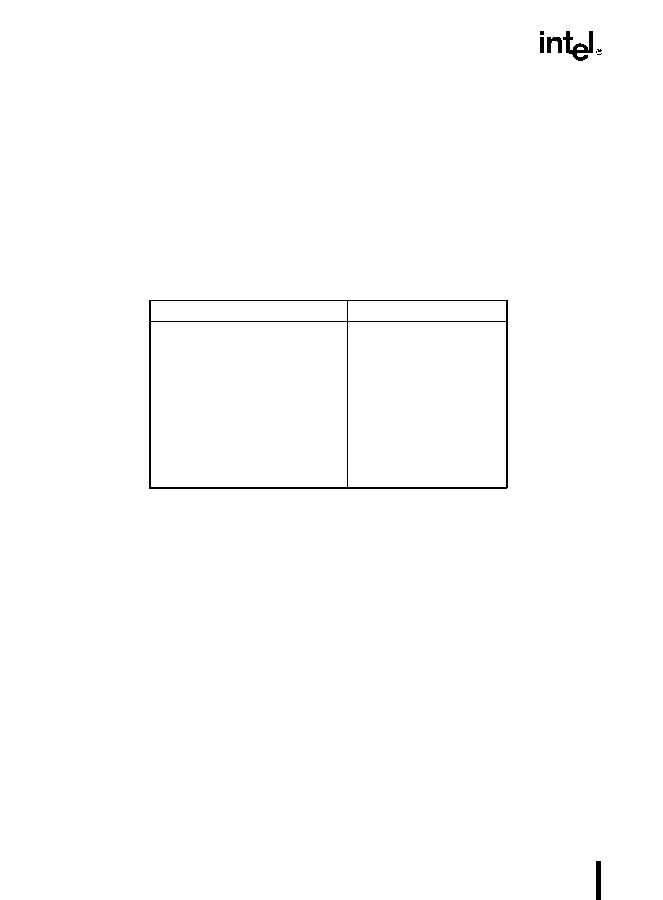

Pseudo-Op

Implementation

CMPEQPS xmm1, xmm2

CMPPS xmm1,xmm2, 0

CMPLTPS xmm1, xmm2

CMPPS xmm1,xmm2, 1

CMPLEPS xmm1, xmm2

CMPPS xmm1,xmm2, 2

CMPUNORDPS xmm1, xmm2CMPPS xmm1,xmm2, 3

CMPNEQPS xmm1, xmm2CMPPS xmm1,xmm2, 4

CMPNLTPS xmm1, xmm2

CMPPS xmm1,xmm2, 5

CMPNLEPS xmm1, xmm2

CMPPS xmm1,xmm2, 6

CMPORDPS xmm1, xmm2CMPPS xmm1,xmm2, 7