3-116

INSTRUCTION SET REFERENCE

CPUIDCPU Identification (Continued)

When the input value is 2, the processor returns information about the processors internal

caches and TLBs in the EAX, EBX, ECX, and EDX registers. The encoding of these registers

is as follows:

The least-significant byte in register EAX (register AL) indicates the number of times the

CPUID instruction must be executed with an input value of 2 to get a complete description

of the processors caches and TLBs. The Pentium

®

Pro family of processors will return a 1.

The most significant bit (bit 31) of each register indicates whether the register contains

valid information (cleared to 0) or is reserved (set to 1).

If a register contains valid information, the information is contained in one-byte

descriptors. Table 3-9 shows the encoding of these descriptors.

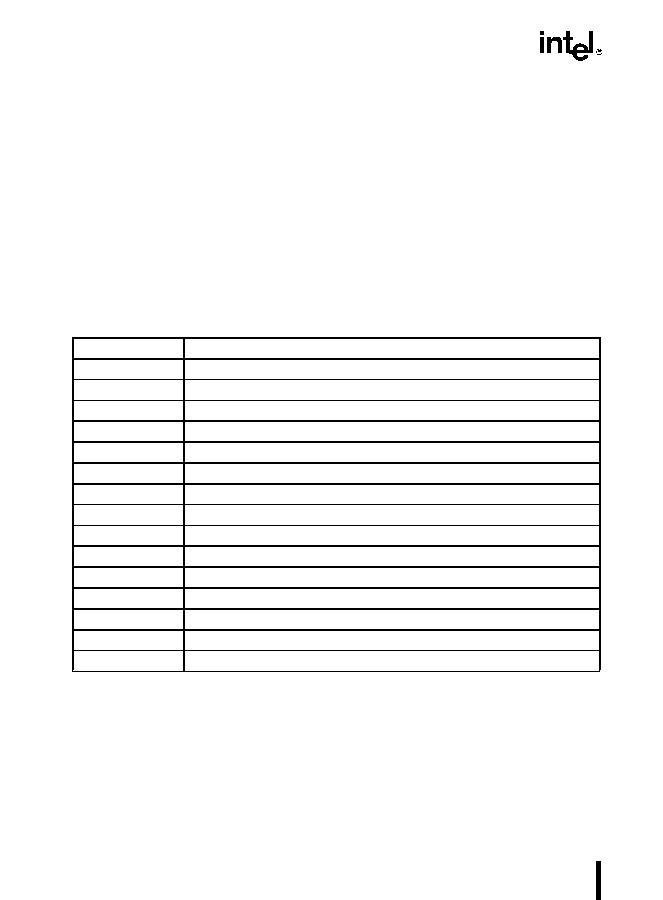

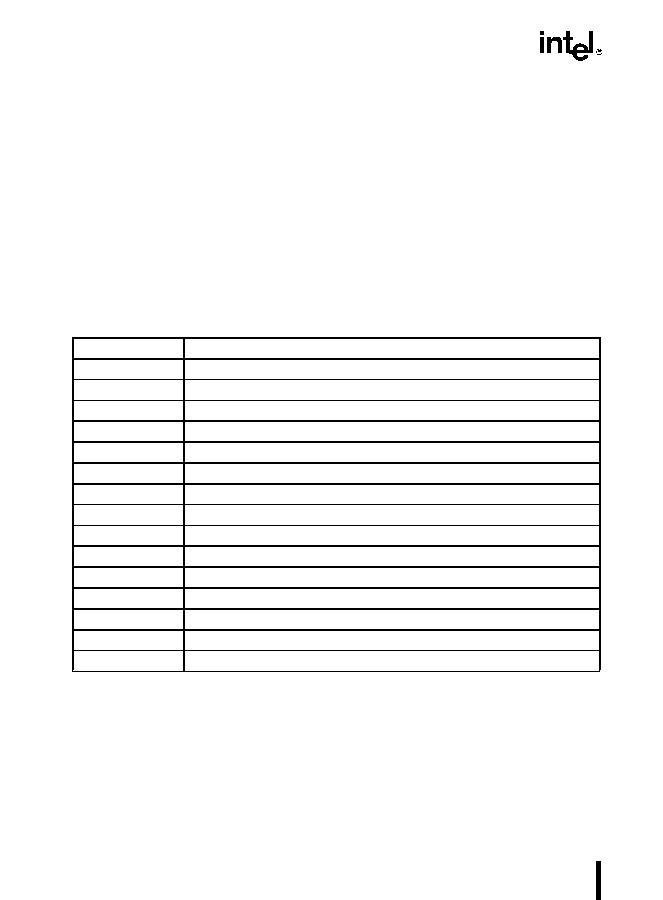

Table 3-9. Encoding of Cache and TLB Descriptors

Descriptor Value

Cache or TLB Description

00H

Null descriptor

01H

Instruction TLB: 4K-Byte Pages, 4-way set associative, 32 entries

02H

Instruction TLB: 4M-Byte Pages, fully associative, two entries

03H

Data TLB: 4K-Byte Pages, 4-way set associative, 64 entries

04H

Data TLB: 4M-Byte Pages, 4-way set associative, eight entries

06H

Instruction cache: 8K Bytes, 4-way set associative, 32 byte line size

08H

Instruction cache: 16K Bytes, 4-way set associative, 32 byte line size

0AH

Data cache: 8K Bytes, 2-way set associative, 32 byte line size

0CH

Data cache: 16K Bytes, 2-way or 4-way set associative, 32 byte line size

40H

No L2 Cache

41H

L2 Unified cache: 128K Bytes, 4-way set associative, 32 byte line size

42H

L2 Unified cache: 256K Bytes, 4-way set associative, 32 byte line size

43H

L2 Unified cache: 512K Bytes, 4-way set associative, 32 byte line size

44H

L2 Unified cache: 1M Byte, 4-way set associative, 32 byte line size

45H

L2 Unified cache: 2M Byte, 4-way set associative, 32 byte line size