A-5

OPCODE MAP

The next part of the SHLD opcode is the 32-bit displacement for the destination memory oper-

and (00000000H), which is followed by the immediate byte representing the count of the shift

(03H). By this breakdown, it has been shown that the opcode 0FA4050000000003H represents

the instruction:

SHLD DS:00000000H, EAX, 3.

Lower case is used in the following tables to highlight the mnemonics added by MMX tech-

nology and Streaming SIMD Extensions.

A.2.3.Opcode Map Shading

Table A-2 contains notes on particular encodings. These notes are indicated in the following Op-

code Maps (Table A-2 through A-6) by superscripts.

For the One-byte Opcode Maps (Table A-2 through A-3), grey shading indicates instruction

groupings.

A.2.4.Opcode Map Notes

Table A-1 contains notes on particular encodings. These notes are indicated in the following Op-

code Maps (Table A-2 through A-6) by superscripts.

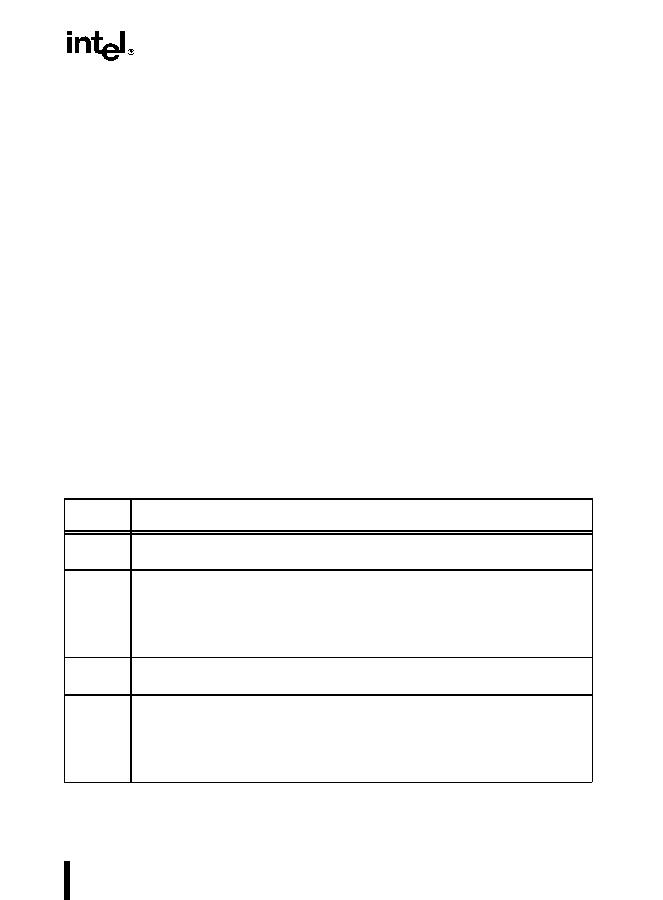

Table A-1. Notes on Instruction Set Encoding Tables

SymbolNote

1A

Bits 5, 4, and 3 of ModR/M byte used as an opcode extension (refer to Section A.2.5.,

Opcode Extensions For One- And Two-byte Opcodes).

1B

These abbreviations are not actual mnemonics. When shifting by immediate shift counts,

the PSHIMD mnemonic represents the PSLLD, PSRAD, and PSRLD instructions,

PSHIMW represents the PSLLW, PSRAW, and PSRLW instructions, and PSHIMQ

represents the PSLLQ and PSRLQ instructions. The instructions that shift by immediate

counts are differentiated by ModR/M bytes (refer to Section A.2.5., Opcode Extensions For

One- And Two-byte Opcodes).

1C

Use the 0F0B opcode (UD2 instruction) or the 0FB9H opcode when deliberately trying to

generate an invalid opcode exception (#UD).

1D

Some instructions added in the Pentium

®

III processor may use the same two-byte opcode.

If the instruction has variations, or the opcode represents different instructions, the ModR/M

byte will be used to differentiate the instruction. For the value of the ModR/M byte needed

to completely decode the instruction, see Table A-6. (These instructions include SFENCE,

STMXCSR, LDMXCSR, FXRSTOR, and FXSAVE, as well as PREFETCH and its

variations.)