B-2

INSTRUCTION FORMATS AND ENCODINGS

Table B-1 lists several smaller fields or bits that appear in certain instructions, sometimes within

the opcode bytes themselves. The following tables describe these fields and bits and list the al-

lowable values. All of these fields (except the d bit) are shown in the integer instruction formats

given in Table B-10.

B.1.1.Reg Field (reg)

The reg field in the ModR/M byte specifies a general-purpose register operand. The group of

registers specified is modified by the presence of and state of the w bit in an encoding (refer to

Table B-4). Table B-2 shows the encoding of the reg field when the w bit is not present in an

encoding, and Table B-3 shows the encoding of the reg field when the w bit is present.

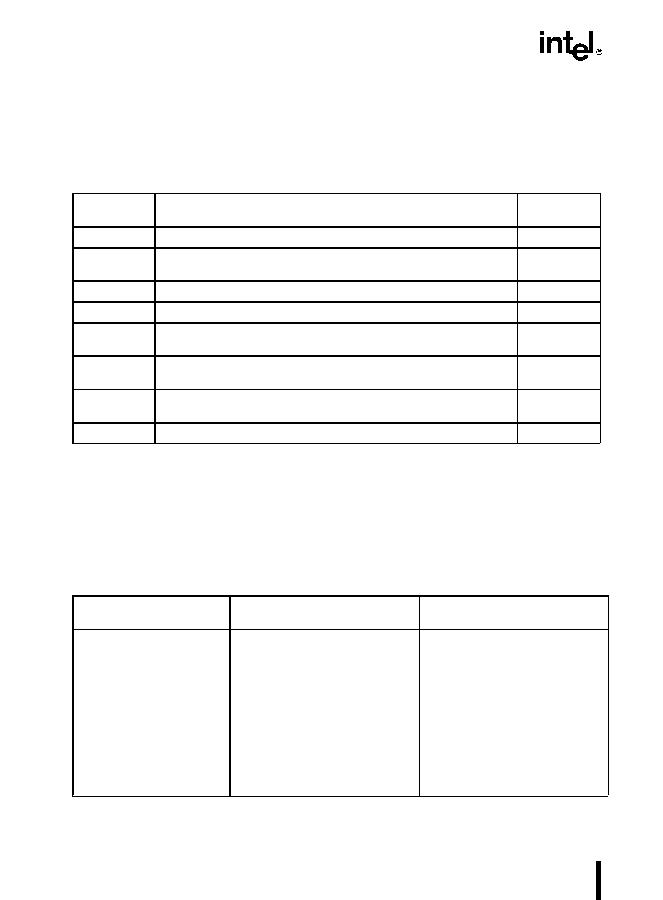

Table B-1. Special Fields Within Instruction Encodings

Field Name

Description

Number of

Bits

reg

General-register specifier (refer to Table B-2 or B-3)

3

w

Specifies if data is byte or full-sized, where full-sized is either 16 or 32

bits (refer to Table B-4)

1

s

Specifies sign extension of an immediate data field (refer to Table B-5)

1

sreg2

Segment register specifier for CS, SS, DS, ES (refer to Table B-6)

2

sreg3

Segment register specifier for CS, SS, DS, ES, FS, GS (refer to Table

B-6)

3

eee

Specifies a special-purpose (control or debug) register (refer to

Table B-7)

3

tttn

For conditional instructions, specifies a condition asserted or a condition

negated (refer to Table B-8)

4

d

Specifies direction of data operation (refer to Table B-9)

1

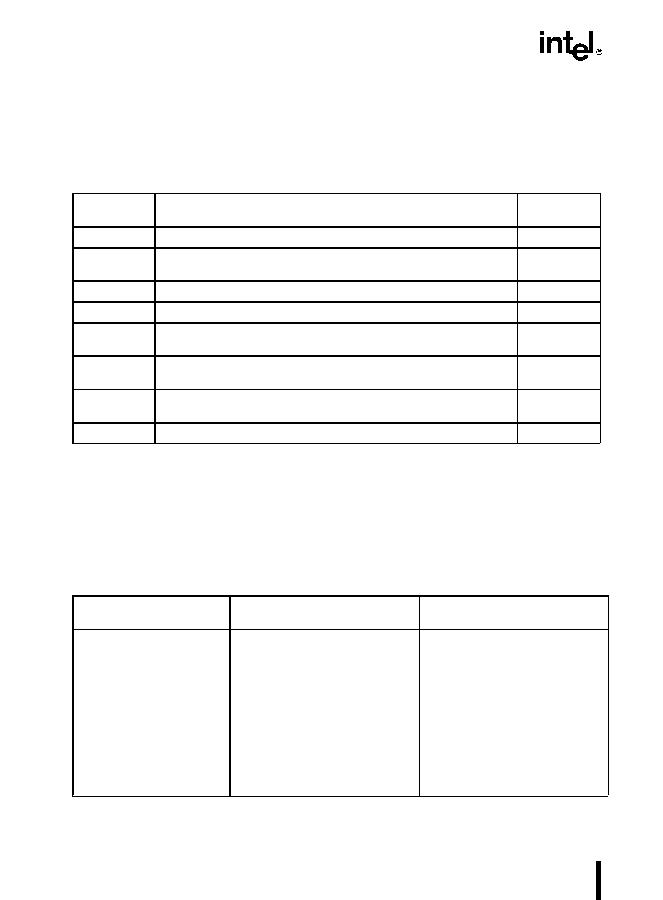

Table B-2. Encoding of reg Field When w Field is Not Present in Instruction

reg Field

Register Selected during

16-Bit Data Operations

Register Selected during

32-Bit Data Operations

000

AX

EAX

001

CX

ECX

010

DX

EDX

011

BX

EBX

100

SP

ESP

101

BP

EBP

110

SI

ESI

111

DI

EDI