B-35

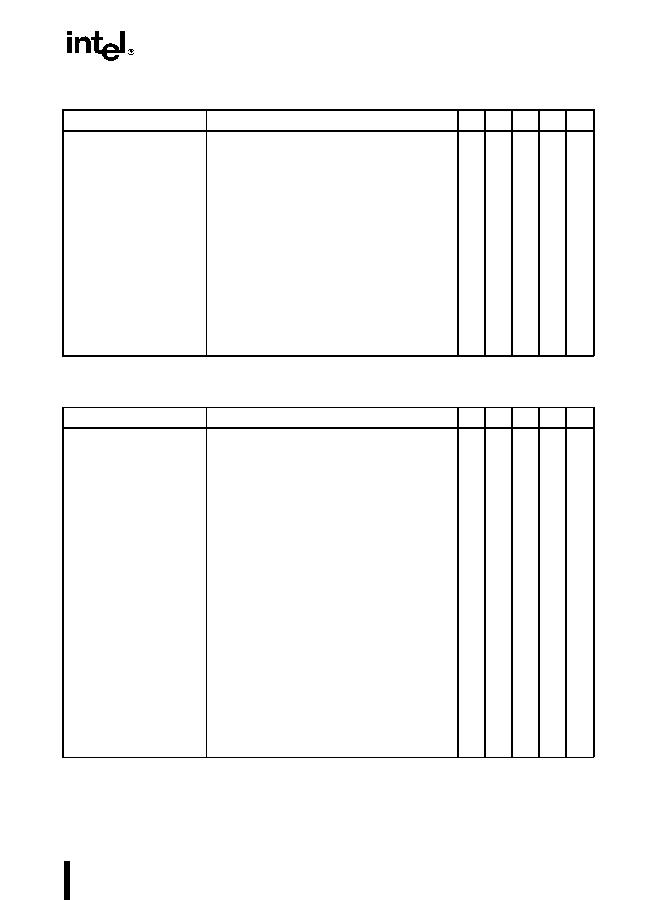

INSTRUCTION FORMATS AND ENCODINGS

PMULHUW - Packed

Multiply High Unsigned

n/aOn/aIn/a

mmreg to mmreg

00001111:11100100:11 mmreg1 mmreg2

mem to mmreg

00001111:11100100 mod mmreg r/m

PSADBW - Packed Sum

of Absolute Differences

IOn/aYn/a

mmreg to mmreg

00001111:11110110:11 mmreg1 mmreg2

mem to mmreg

00001111:11110110 mod mmreg r/m

PSHUFW - Packed

Shuffle Word

n/aYn/aIn/a

mmreg to mmreg, imm800001111:01110000:11 mmreg1 mmreg2: imm8

mem to mmreg, imm800001111:01110000:11 mod mmreg r/m: imm8

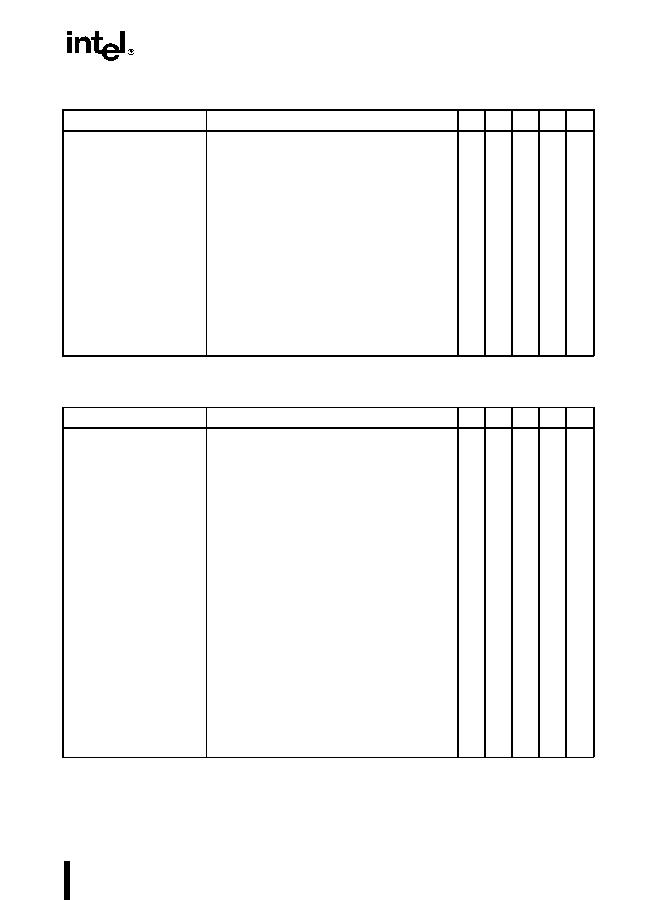

Table B-21. Encoding of the Streaming SIMD Extensions

Cacheability Control Register Field

Instruction and Format

Encoding

BWDQDQ

MASKMOVQ - Byte Mask

Write

n/an/an/aYn/a

mmreg to mmreg

00001111:11110111:11 mmreg1 mmreg2

MOVNTPS - Move

Aligned Four Packed

Single-FP Non Temporal

n/an/an/an/aY

xmmreg to mem

00001111:00101011 mod xmmreg r/m

MOVNTQ - Move 64 Bits

Non Temporal

n/an/an/aYn/a

mmreg to mem

00001111:11100111 mod mmreg r/m

PREFETCHT0 - Prefetch

to all cache levels

00001111:00011000:01 mem

YYYYY

PREFETCHT1 - Prefetch

to all cache levels

00001111:00011000:10 mem

YYYYY

PREFETCHT2 - Prefetch

to L2 cache

00001111:00011000:11 mem

YYYYY

PREFETCHNTA -

Prefetch to L1 cache

00001111:00011000:00 mem

YYYYY

SFENCE - Store Fence00001111:10101110:11111000

YYYYY

Table B-20. Encoding of the SIMD-Integer Register Field

Instruction and Format

Encoding

BWDQDQ