3-2

BASIC EXECUTION ENVIRONMENT

3.2.OVERVIEW OF THE BASIC EXECUTION ENVIRONMENT

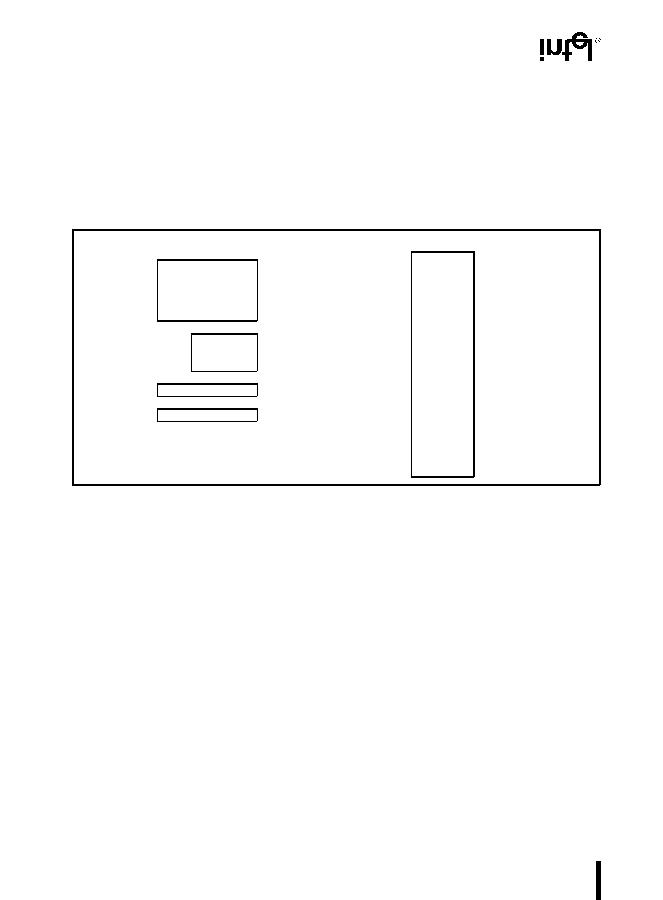

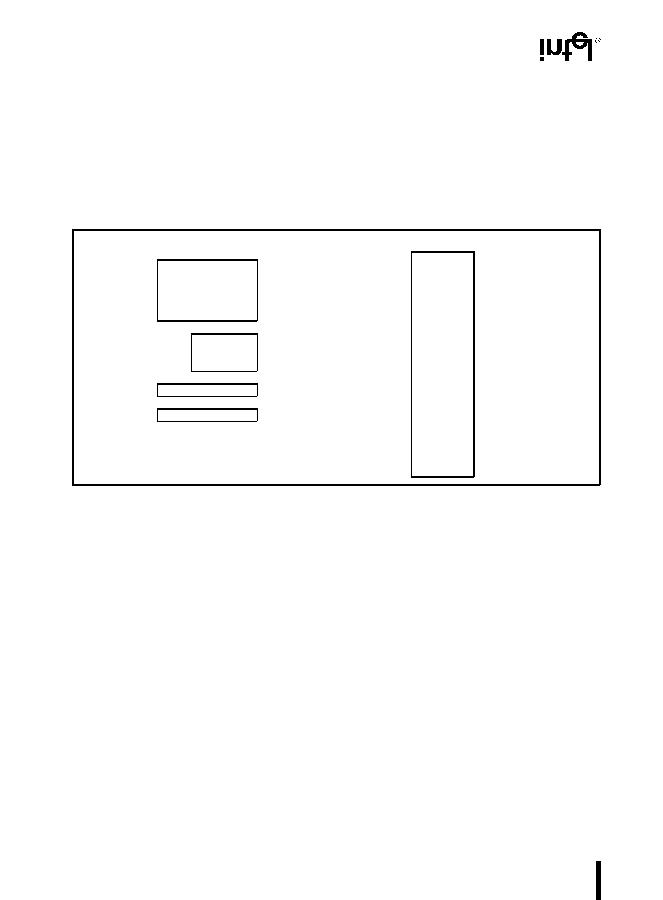

Any program or task running on an IA processor is given a set of resources for executing instruc-

tions and for storing code, data, and state information. These resources (shown in Figure 3-1)

include an address space of up to 2

36

bytes, a set of general data registers, a set of segment regis-

ters, and a set of status and control registers. When a program calls a procedure, a procedure

stack is added to the execution environment. (Procedure calls and the procedure stack imple-

mentation are described in Chapter 4, Procedure Calls, Interrupts, and Exceptions.)

3.3.MEMORY ORGANIZATION

The memory that the processor addresses on its bus is called physical memory. Physical

memory is organized as a sequence of 8-bit bytes. Each byte is assigned a unique address, called

a physical address. The physical address space ranges from zero to a maximum of 2

36

1

(64 gigabytes).

Virtually any operating system or executive designed to work with an IA processor will use the

processors memory management facilities to access memory. These facilities provide features

such as segmentation and paging, which allow memory to be managed efficiently and reliably.

Memory management is described in detail in Chapter 3, Protected-Mode Memory Manage-

ment, of the Intel Architecture Software Developers Manual, Volume 3. The following para-

graphs describe the basic methods of addressing memory when memory management is used.

When employing the processors memory management facilities, programs do not directly

address physical memory. Instead, they access memory using any of three memory models: flat,

segmented, or real-address mode.

With the flat memory model (refer to Figure 3-2), memory appears to a program as a single,

continuous address space, called a linear address space. Code (a programs instructions), data,

Figure 3-1. P6 Family Processor Basic Execution Environment

0

2

36

?

1

Eight 32-bit

32-bits

32-bits

General-Purpose

Registers

Segment Registers

EFLAGS Register

EIP (Instruction

Pointer Register)

Space*

Address

*The address space can be flat or segmented.

Six 16-bit

Registers

Registers

* Physical address space is 2**36-1

* Linear address space is 2**32-1