7-13

FLOATING-POINT UNIT

point instructions set the condition code flags. These condition code bits are used principally for

conditional branching and for storage of information used in exception handling (refer to

Section 7.3.3., Branching and Conditional Moves on FPU Condition Codes).

As shown in Table 7-3, the C1 condition code flag is used for a variety of functions. When both

the IE and SF flags in the FPU status word are set, indicating a stack overflow or underflow

exception (#IS), the C1 flag distinguishes between overflow (C1=1) and underflow (C1=0).

When the PE flag in the status word is set, indicating an inexact (rounded) result, the C1 flag is

set to 1 if the last rounding by the instruction was upward. The FXAM instruction sets C1 to the

sign of the value being examined.

The C2 condition code flag is used by the FPREM and FPREM1 instructions to indicate an

incomplete reduction (or partial remainder). When a successful reduction has been completed,

the C0, C3, and C1 condition code flags are set to the three least-significant bits of the quotient

(Q2, Q1, and Q0, respectively). Refer to FPREM1Partial Remainder in Chapter 3, Instruc-

tion Set Reference, of the Intel Architecture Software Developers Manual, Volume 2, for more

information on how these instructions use the condition code flags.

The FPTAN, FSIN, FCOS, and FSINCOS instructions set the C2 flag to 1 to indicate that the

source operand is beyond the allowable range of ±2

63

.

Where the state of the condition code flags are listed as undefined in Table 7-3, do not rely on

any specific value in these flags.

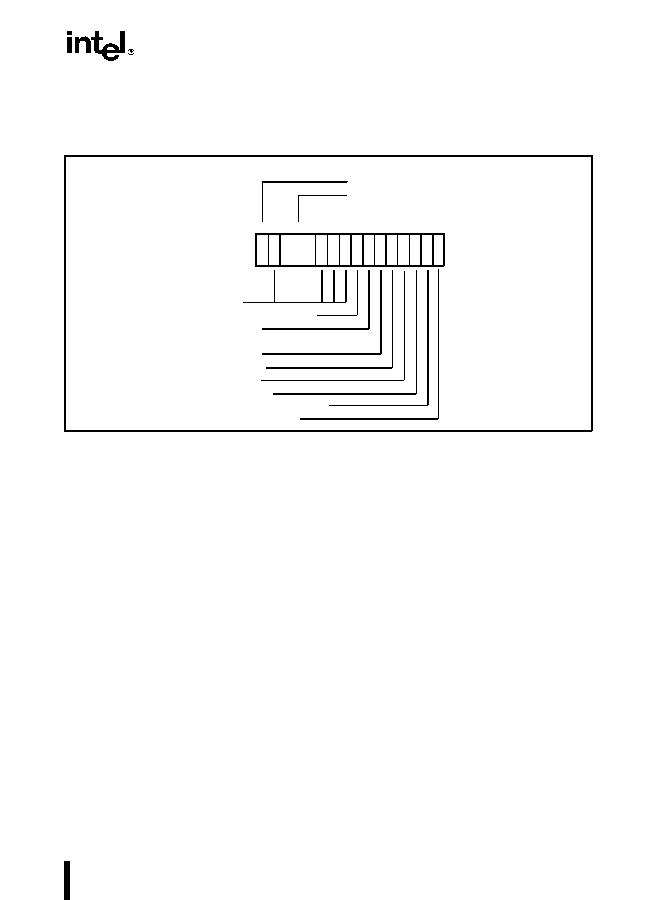

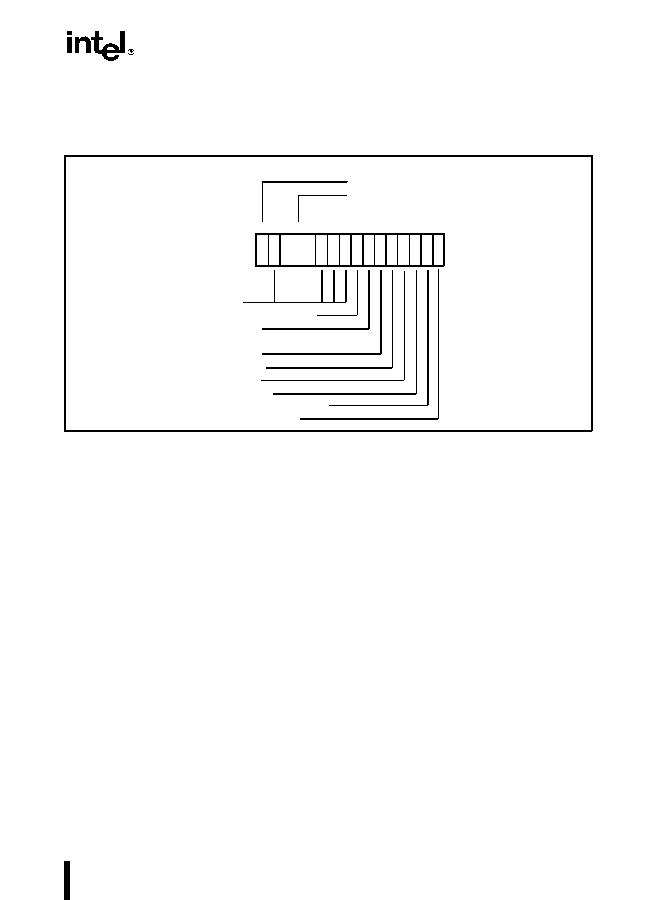

Figure 7-8. FPU Status Word

FPU Busy

1513

1411109876543210

B

I

E

P

E

O

E

U

E

Z

E

D

E

TOP

Top of Stack Pointer

Exception Flags

Precision

Underflow

Overflow

Zero Divide

Denormalized Operand

Invalid Operation

Stack Fault

Error Summary Status

Condition

Code

C

2

C

1

C

0

E

S

S

F

C

3