7-17

FLOATING-POINT UNIT

7.3.4.1.EXCEPTION-FLAG MASKS

The exception-flag mask bits (bits 0 through 5 of the FPU control word) mask the 6 exception

flags in the FPU status word (also bits 0 through 5). When one of these mask bits is set, its corre-

sponding floating-point exception is blocked from being generated.

7.3.4.2.PRECISION CONTROL FIELD

The precision-control (PC) field (bits 8 and 9 of the FPU control word) determines the precision

(64, 53, or 24 bits) of floating-point calculations made by the FPU (refer to Table 7-4). The

default precision is extended precision, which uses the full 64-bit significand available with the

extended-real format of the FPU data registers, but is configurable by the user, compiler, or oper-

ating system. This setting is best suited for most applications, because it allows applications to

take full advantage of the precision of the extended-real format.

NOTE:

*

Includes the implied integer bit.

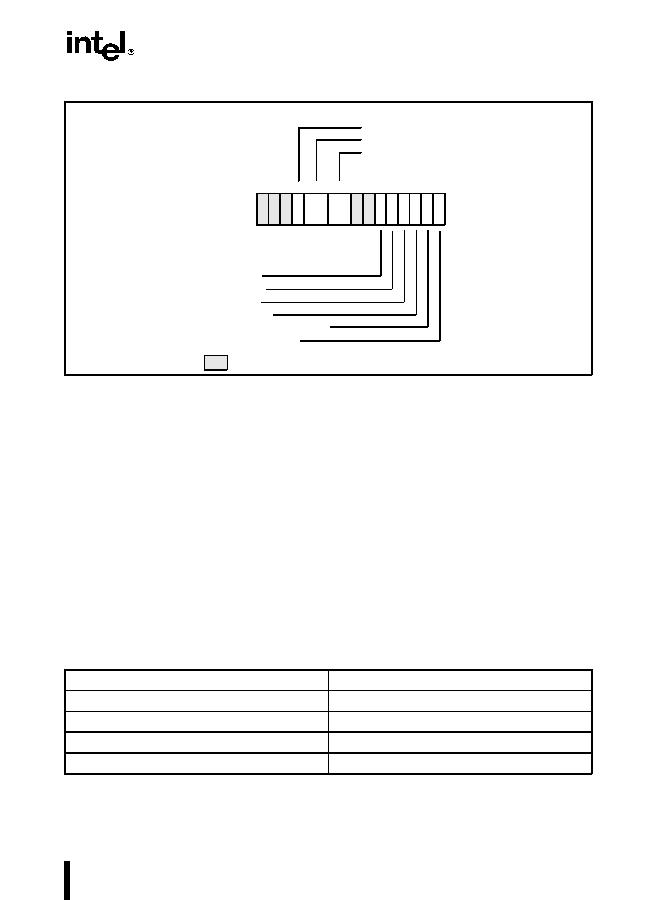

Figure 7-10. FPU Control Word

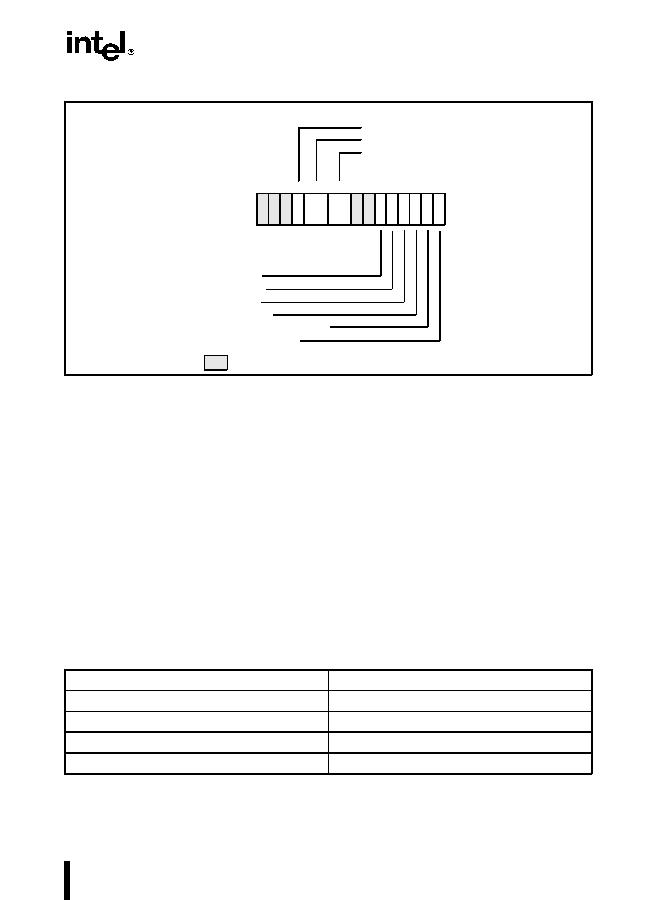

Table 7-4. Precision Control Field (PC)

Precision

PC Field

Single Precision (24-Bits

*

)

00B

Reserved

01B

Double Precision (53-Bits

*

)

10B

Extended Precision (64-Bits)

11B

1513

141211109876543210

X

I

M

P

M

O

M

U

M

Z

M

D

M

RCPC

Infinity Control

Rounding Control

Precision Control

Exception Masks

Precision

Underflow

Overflow

Zero Divide

Denormalized Operand

Invalid Operation

Reserved