7-53

FLOATING-POINT UNIT

Section 7.7.3., Software Exception Handling) and the top-of-stack pointer (TOP) and source

operands remain unchanged.

7.8.2.Divide-By-Zero Exception (#Z)

The FPU reports a floating-point zero-divide exception whenever an instruction attempts to

divide a finite non-zero operand by 0. The flag (ZE) for this exception is bit 2 of the FPU status

word, and the mask bit (ZM) is bit 2 of the FPU control word. The FDIV, FDIVP, FDIVR,

FDIVRP, FIDIV, and FIDIVR instructions and the other instructions that perform division inter-

nally (FYL2X and FXTRACT) can report the divide-by-zero exception.

When a divide-by-zero exception occurs and the exception is masked, the FPU sets the ZE flag

and returns the values shown in Table 7-21. If the divide-by-zero exception is not masked, the

ZE flag is set, a software exception handler is invoked (refer to Section 7.7.3., Software Excep-

tion Handling), and the top-of-stack pointer (TOP) and source operands remain unchanged.

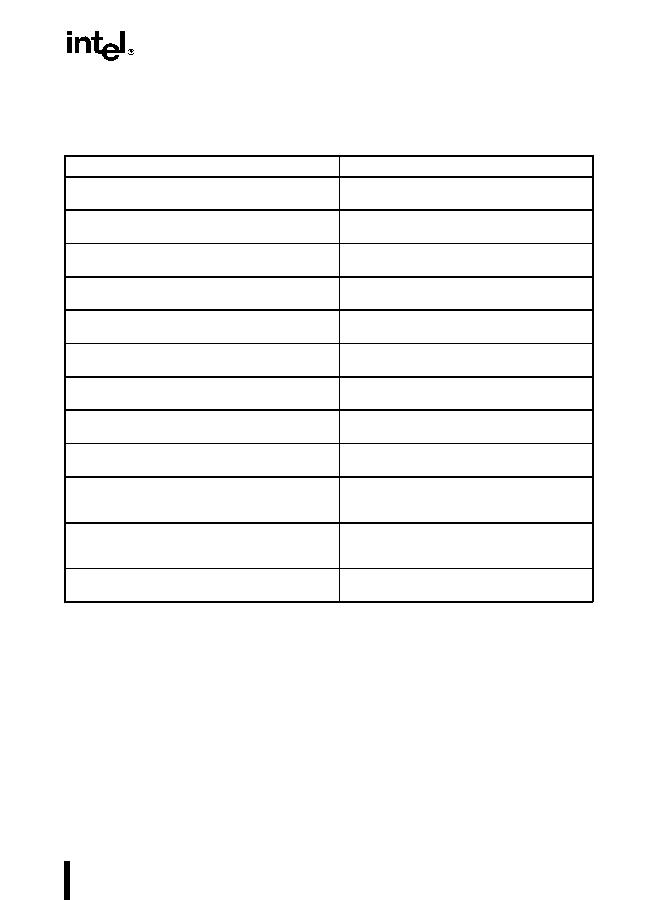

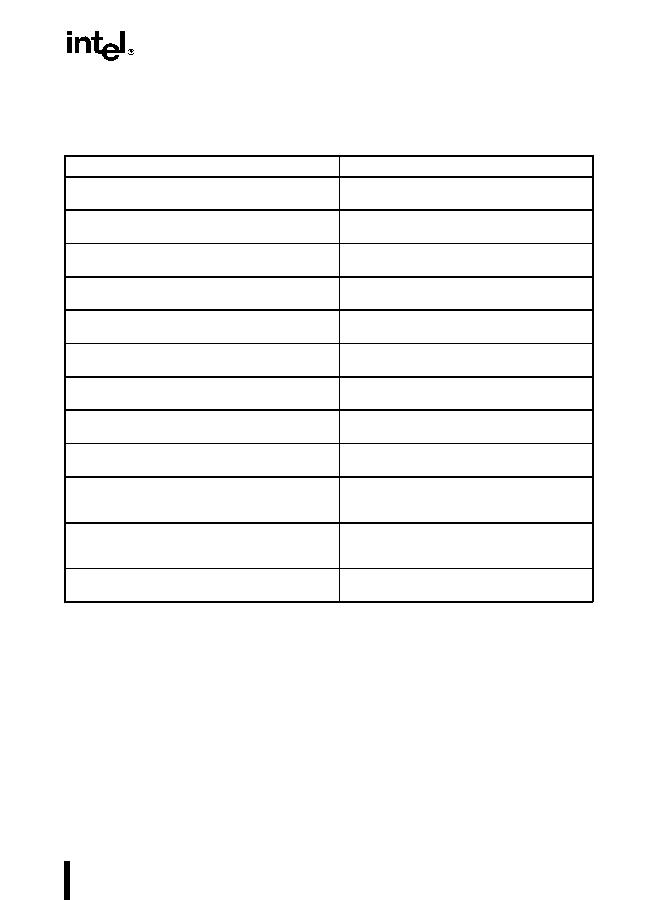

Table 7-21. Invalid Arithmetic Operations and the Masked Responses to Them

Condition

Masked Response

Any arithmetic operation on an operand that is in an

unsupported format.

Return the real indefinite value to the destination

operand.

Any arithmetic operation on a SNaN.

Return a QNaN to the destination operand (refer

to Section 7.6., Operating on NaNs).

Compare and test operations: one or both operands

are NaNs.

Set the condition code flags (C0, C2, and C3) in

the FPU status word to 111B (not comparable).

Addition: operands are opposite-signed infinities.

Subtraction: operands are like-signed infinities.

Return the real indefinite value to the destination

operand.

Multiplication:

?

by 0; 0 by

?

.

Return the real indefinite value to the destination

operand.

Division:

?

by

?

; 0 by 0.

Return the real indefinite value to the destination

operand.

Remainder instructions FPREM, FPREM1: modulus

(divisor) is 0 or dividend is

?

.

Return the real indefinite; clear condition code

flag C2 to 0.

Trigonometric instructions FCOS, FPTAN, FSIN,

FSINCOS: source operand is

?

.

Return the real indefinite; clear condition code

flag C2 to 0.

FIST/FISTP instruction when input operand <>

MAXINT for destination operand size.

Return MAXNEG to destination operand.

FSQRT: negative operand (except FSQRT (0) = 0);

FYL2X: negative operand (except FYL2X (0) =

?

);

FYL2XP1: operand more negative than 1.

Return the real indefinite value to the destination

operand.

FBSTP: source register is empty or it contains a NaN,

?

, or a value that cannot be represented in 18

decimal digits.

Store BCD integer indefinite value in the

destination operand.

FXCH: one or both registers are tagged empty.Load empty registers with the real indefinite

value, then perform the exchange.