8-10

PROGRAMMING WITH THE INTEL MMX TECHNOLOGY

words, or doublewords contained in a 64-bit MMX register, as described in the following

section (Section 8.1.3., Single Instruction, Multiple Data (SIMD) Execution Model).

When operating on the bytes, words, and doublewords within packed data types, the MMX

instructions recognize and operate on both signed and unsigned byte integers, word integers, and

doubleword integers.

8.1.3.Single Instruction, Multiple Data (SIMD) Execution Model

The MMX technology uses the single instruction, multiple data (SIMD) technique for

performing arithmetic and logical operations on the bytes, words, or doublewords packed into

64-bit MMX registers. For example, the PADDSB instruction adds 8 signed bytes from the

source operand to 8 signed bytes in the destination operand and stores 8 byte-results in the desti-

nation operand. This SIMD technique speeds up software performance by allowing the same

operation to be carried out on multiple data elements in parallel. The MMX technology

supports parallel operations on byte, word, and doubleword data elements when contained in

MMX registers.

The SIMD execution model supported in the MMX technology directly addresses the needs

of modern media, communications, and graphics applications, which often use sophisticated

algorithms that perform the same operations on a large number of small data types (bytes, words,

and doublewords). For example, most audio data is represented in 16-bit (word) quantities. The

MMX instructions can operate on 4 of these words simultaneously with one instruction. Video

and graphics information is commonly represented as palletized 8-bit (byte) quantities. Here,

one MMX instruction can operate on 8 of these bytes simultaneously.

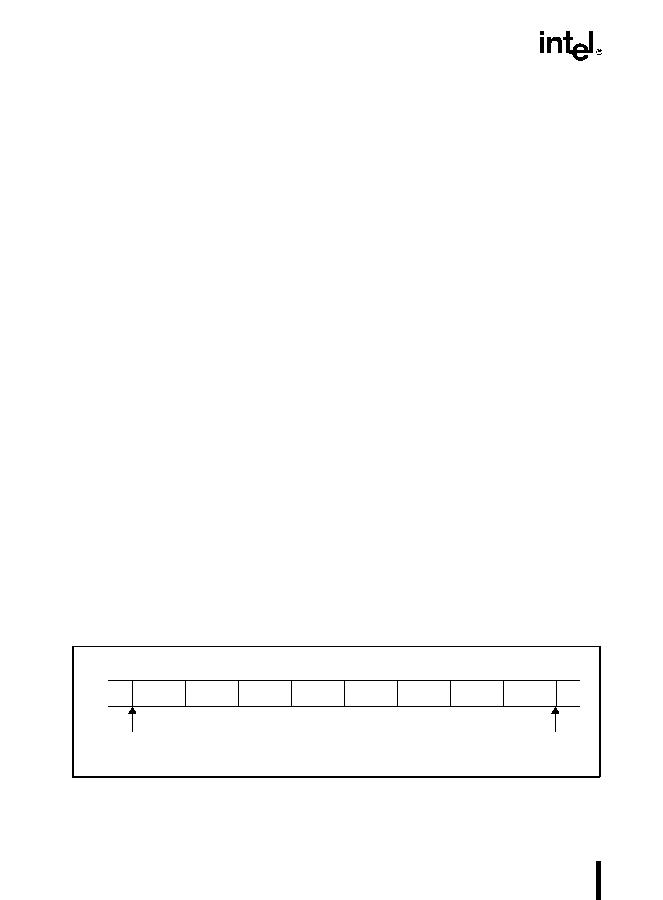

8.1.4.Memory Data Formats

When stored in memory the bytes, words, and doublewords in the packed data types are stored

in consecutive addresses, with the least significant byte, word, or doubleword being stored in

the lowest address and the more significant bytes, words, or doubleword being stored at consec-

utively higher addresses (refer to Figure 8-3). The ordering bytes, words, or doublewords in

memory is always little endian. That is, the bytes with the lower addresses are less significant

than the bytes with the higher addresses.

Figure 8-3. Eight Packed Bytes in Memory (at address 1000H)

3006045

63

0

Byte 7Byte 6Byte 5Byte 4Byte 3Byte 2Byte 1Byte 0

56554847403932312423161587

Memory Address 1008h

Memory Address 1000h