8-11

PROGRAMMING WITH THE INTEL MMX TECHNOLOGY

8.1.2.MMX Data Types

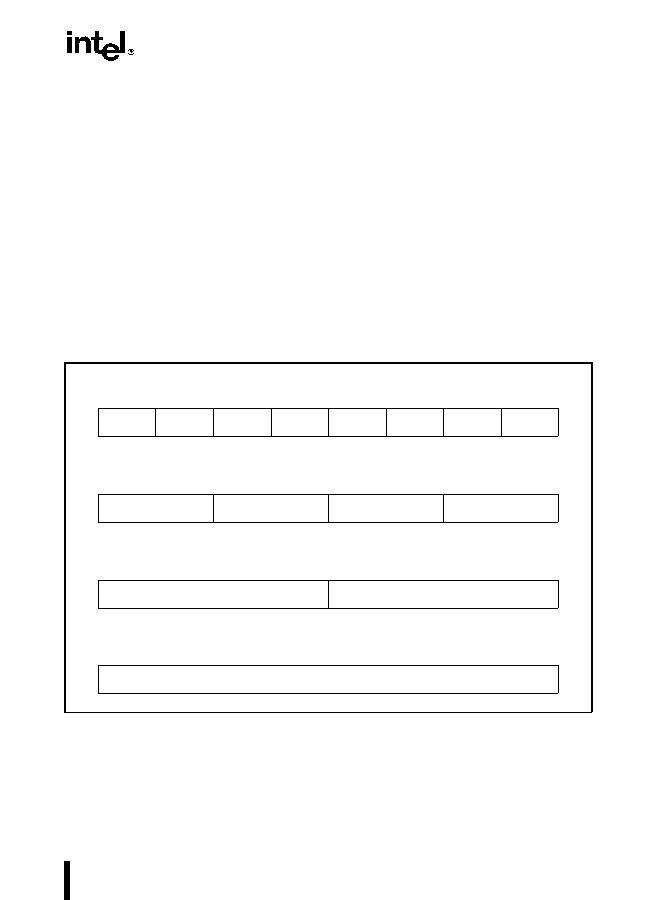

The MMX technology defines the following new 64-bit data types (refer to Figure 8-2):

Packed bytes

Eight bytes packed into one 64-bit quantity.

Packed words

Four (16-bit) words packed into one 64-bit quantity.

Packed doublewordsTwo (32-bit) doublewords packed into one 64-bit quantity.

Quadword

One 64-bit quantity.

The bytes in the packed bytes data type are numbered 0 through 7, with byte 0 being contained

in the least significant bits of the data type (bits 0 through 7) and byte 7 being contained in the

most significant bits (bits 56 through 63). The words in the packed words data type are

numbered 0 through 4, with word 0 being contained in the bits 0 through 15 of the data type and

word 4 being contained in bits 48 through 63. The doublewords in a packed doublewords data

type are numbered 0 and 1, with doubleword 0 being contained in bits 0 through 31 and double-

word 1 being contained in bits 32 through 63.

The MMX instructions move the packed data types (packed bytes, packed words, or packed

doublewords) and the quadword data type to-and-from memory or to-and-from the IA general-

purpose registers in 64-bit blocks. However, when performing arithmetic or logical operations

on the packed data types, the MMX instructions operate in parallel on the individual bytes,

Figure 8-2. MMX Data Types

3006002

63

Packed bytes (8x8 bits)

56 5548 4740 3932 3124 2316 158 70

63

Packed word (4x16 bits)

48 47

32 31

16 15

0

63

Packed doublewords (2x32 bits)

32 31

0

63

Quadword (64 bits)

0