9-10

PROGRAMMING WITH THE STREAMING SIMD EXTENSIONS

9.3.OVERVIEW OF THE STREAMING SIMD EXTENSIONS SET

Appendix D, SIMD Floating-Point Exceptions Summary shows the instructions in the

Streaming SIMD Extensions set. The following sections give a brief overview of each group of

instructions in the Streaming SIMD Extensions set and the instructions within each group.

9.3.1.Data Movement Instructions

The MOVAPS (Move aligned packed, single-precision, floating-point) instruction transfers 128

bits of packed data from memory to SIMD floating-point registers and vice versa, or between

SIMD floating-point registers. The memory address is aligned to 16-byte boundary; otherwise,

a general protection exception will occur.

The MOVUPS (Move unaligned packed, single-precision, floating-point) instruction transfers

128 bits of packed data from memory to SIMD floating-point registers and vice versa, or

between SIMD floating-point registers. No assumption is made for alignment.

The MOVHPS (Move unaligned, high packed, single-precision, floating-point) instruction

transfers 64 bits of packed data from memory to the upper two fields of a SIMD floating-point

register and vice versa. The lower two fields are left unchanged.

The MOVHLPS (Move high to low packed, single-precision, floating-point) instruction trans-

fers the upper 64-bits of the source register into the lower 64-bits of the 128-bit destination

register. The upper 64-bits of the destination register are left unchanged.

The MOVLHPS (Move low to high packed, single-precision, floating-point) instruction trans-

fers the lower 64-bits of the source register into the upper 64-bits of the 128-bit destination

register. The lower 64-bits of the destination register are left unchanged.

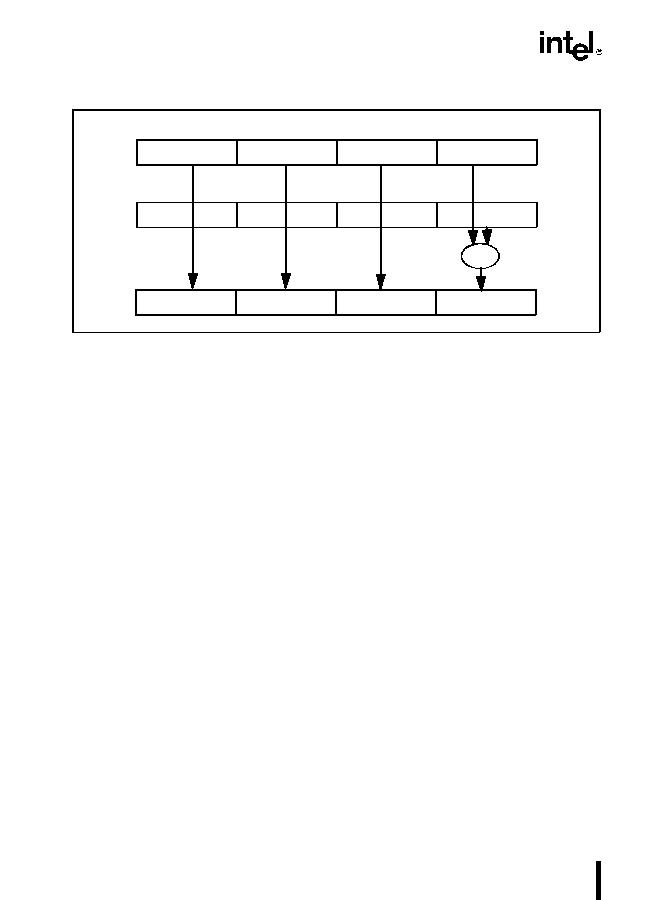

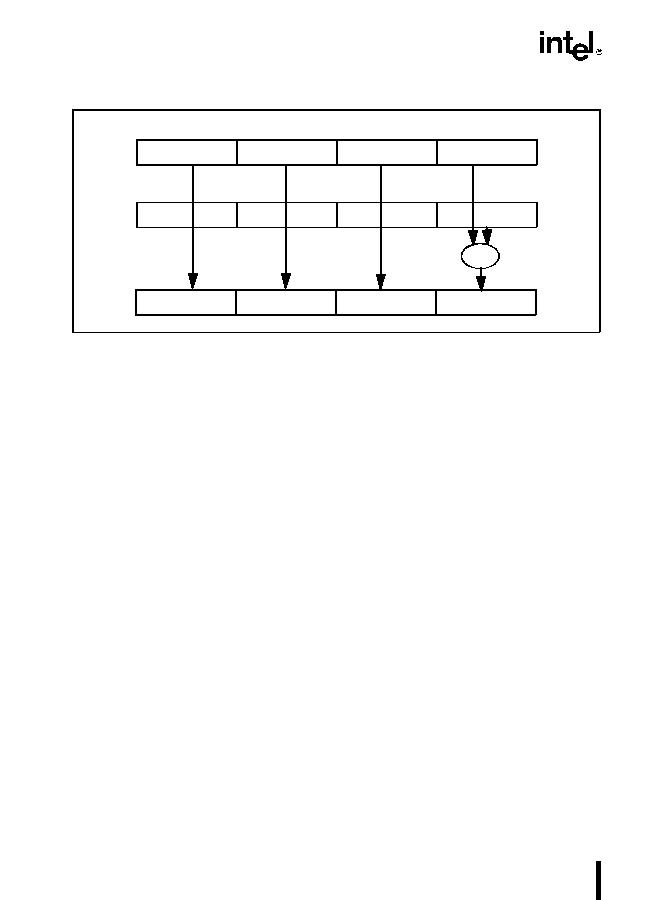

Figure 9-6. Scalar Operations

X1 (SP) X2 (SP)

X3 (SP)

X4 (SP)

Y1 (SP)Y2 (SP)

Y3 (SP)

Y4 (SP)

X1 (SP) X2 (SP)

X3 (SP)X4 op Y4 (SP)

OP