10-7

INPUT/OUTPUT

order. Refer to Chapter 9, Memory Cache Control, in the Intel Architecture Software Devel-

opers Manual, Volume 3, for more information on using MTRRs.

Another method of enforcing program order is to insert one of the serializing instructions, such

as the CPUID instruction, between operations. Refer to Chapter 7, Multiple-Processor Manage-

ment, in the Intel Architecture Software Developers Manual, Volume 3, for more information on

serialization of instructions.

It should be noted that the chip set being used to support the processor (bus controller, memory

controller, and/or I/O controller) may post writes to uncacheable memory which can lead to out-

of-order execution of memory accesses. In situations where out-of-order processing of memory

accesses by the chip set can potentially cause faulty memory-mapped I/O processing, code must

be written to force synchronization and ordering of I/O operations. Serializing instructions can

often be used for this purpose.

When the I/O address space is used instead of memory-mapped I/O, the situation is different in

two respects:

The processor never buffers I/O writes. Therefore, strict ordering of I/O operations is

enforced by the processor. (As with memory-mapped I/O, it is possible for a chip set to

post writes in certain I/O ranges.)

The processor synchronizes I/O instruction execution with external bus activity (refer to

Table 10-1).

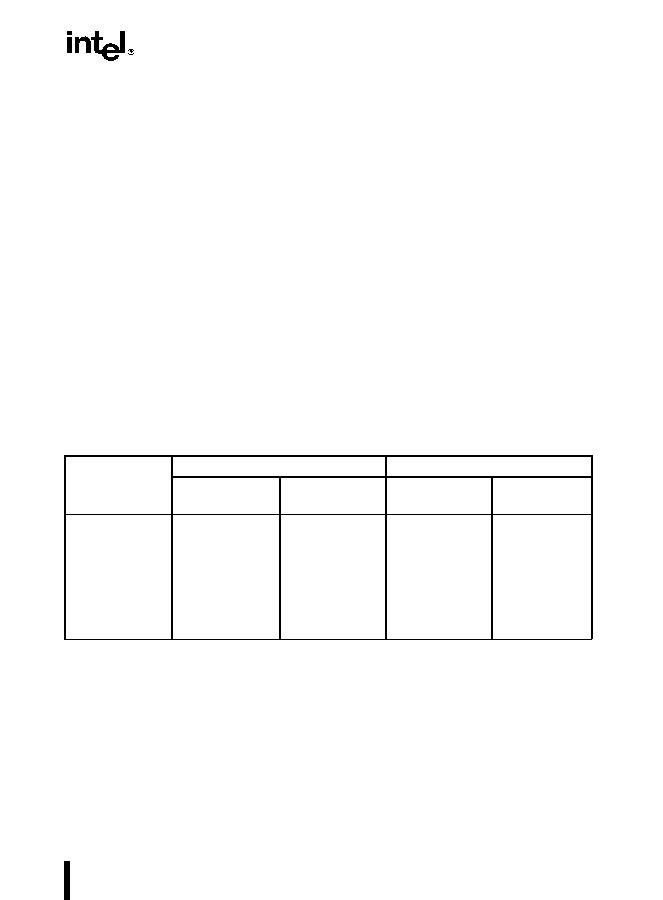

Table 10-1. I/O Instruction Serialization

Instruction Being

Executed

Processor Delays Execution of

Until Completion of

Current

Instruction?Next Instruction?Pending Stores?Current Store?

IN

Yes

Yes

INS

Yes

Yes

REP INS

Yes

Yes

OUT

Yes

Yes

Yes

OUTS

Yes

Yes

Yes

REP OUTS

Yes

Yes

Yes