E-24

GUIDELINES FOR WRITING FPU EXCEPTIONS HANDLERS

When the FNSAVE starts, it will trigger an interrupt via FERR# because of the pending numeric

exception. After some system dependent delay, the numeric exception handler is entered. It may

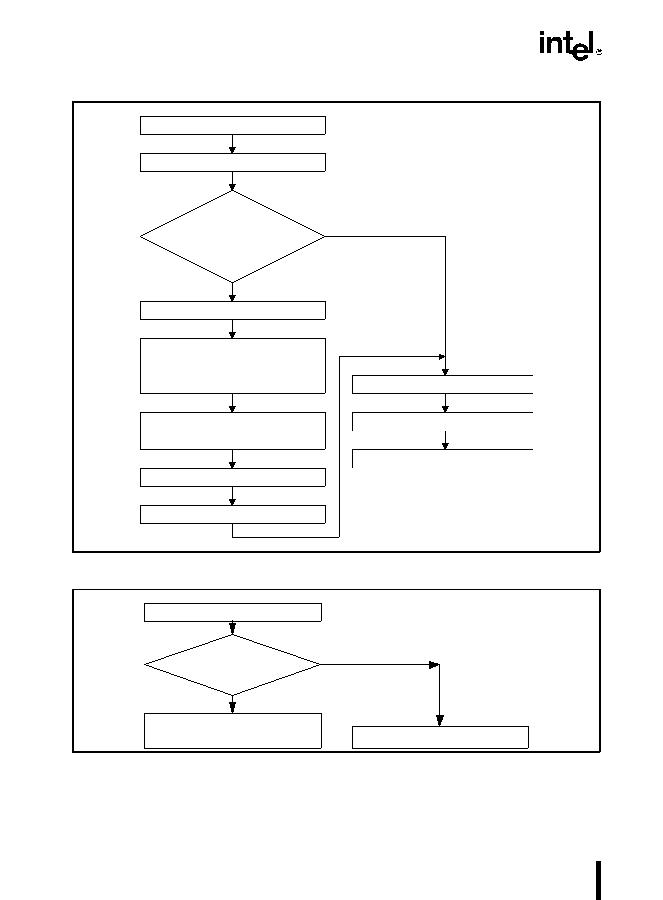

Figure E-5. General Program Flow for DNA Exception Handler

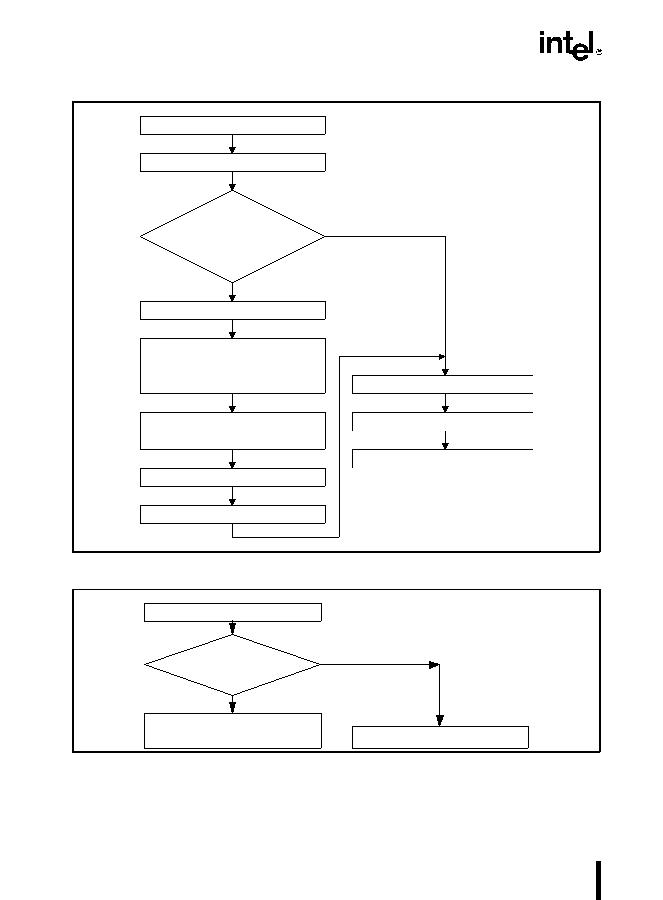

Figure E-6. Program Flow for a Numeric Exception Dispatch Routine

Current Thread

same as

FPU Owner?

DNA Handler Entry

<other handler setup code>

FPU Owner = Kernel

Use FNSAVE or FXSAVE to Old

Threads FP Save Area

(may cause numeric exception)

Use FRSTOR or FXRSTOR from

Current Threads FP Save Area

<other handler code>

FPU Owner = Current Thread

<handler final cleanup>

CLTS (clears CR0.TS)

Exit DNA Handler

Yes

No

Numeric Exception Entry

Is Kernel

FPU Owner?

Normal Dispatch to

Numeric Exception Handler

Exit

No

Yes