F-8

GUIDELINES FOR WRITING SIMD FLOATING-POINT EXCEPTION

Note 1. SNaN | 0x00400000 is a quiet NaN obtained from the signaling NaN given as input

Note 2. Operations involving only quiet NaNs do not raise a floating-point exception

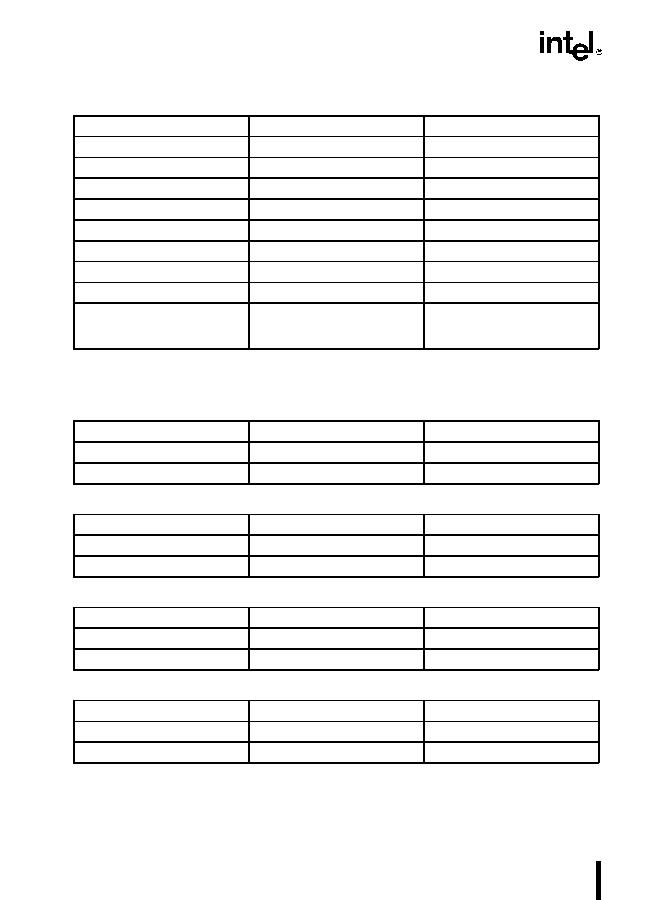

Table F-1. ADDPS, ADDSS, SUBPS, SUBSS, MULPS, MULSS, DIVPS, DIVSS

Source Operands

Masked Result

Unmasked Result

SNaN1 op SNaN2

SNaN1 | 0x00400000

None

SNaN1 op QNaN2

SNaN1 | 0x00400000

None

QNaN1 op SNaN2

QNaN1

None

QNaN1 op QNaN2

QNaN1

QNaN1 (not an exception)

SNaN op real value

SNaN | 0x00400000

None

Real value op SNaN

SNaN | 0x00400000

None

QNaN op real value

QNaN

QNaN (not an exception)

Real value op QNaN

QNaN

QNaN (not an exception)

Neither source operand is SNaN,

but #I is signaled (e.g. for Inf - Inf,

Inf * 0, Inf / Inf, 0/0)

Single-Precision QNaN Indefinite

None

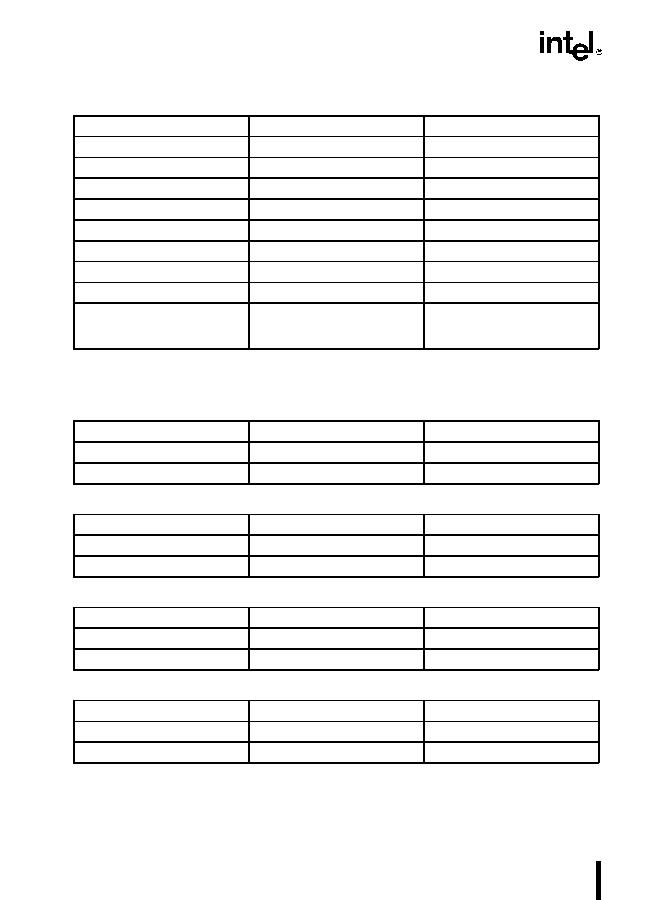

Table F-2. CMPPS.EQ, CMPSS.EQ, CMPPS.ORD, CMPSS.ORD

Source Operands

Masked Result

Unmasked Result

NaN op Opd2 (any Opd2)

0x00000000

0x00000000 (not an exception)

Opd1 op NaN (any Opd1)

0x00000000

0x00000000 (not an exception)

Table F-3. CMPPS.NEQ, CMPSS.NEQ, CMPPS.UNORD, CMPSS.UNORD

Source Operands

Masked Result

Unmasked Result

NaN op Opd2 (any Opd2)

0x11111111

0x11111111 (not an exception)

Opd1 op NaN (any Opd1)

0x11111111

0x11111111 (not an exception)

Table F-4. CMPPS.LT, CMPSS.LT, CMPPS.LE, CMPSS.LE

Source Operands

Masked Result

Unmasked Result

NaN op Opd2 (any Opd2)

0x00000000

None

Opd1 op NaN (any Opd1)

0x00000000

None

Table F-5. CMPPS.NLT, CMPSS.NLT, CMPSS.NLT, CMPSS.NLE

Source Operands

Masked Result

Unmasked Result

NaN op Opd2 (any Opd2)

0x11111111

None

Opd1 op NaN (any Opd1)

0x11111111

None